Piirilevyviat ovat harvoin satunnaisia.

Useimmissa tapauksissa epäonnistumiset johtuvat seuraavista syistä suunnittelupäätökset, materiaalivalinnat tai valmistusprosessin rajoitukset..

Yleisten piirilevyjen vikamuotojen ymmärtäminen auttaa insinöörejä:

- Tunnistetaan perimmäiset syyt nopeammin

- Parannetaan valmistettavuuden suunnittelua (DFM).

- Vähentää kenttävikoja ja takuukustannuksia

Tässä artikkelissa annetaan käytännönläheinen katsaus yleisimpiin piirilevyjen vikoihin, niiden oireisiin ja siihen, miten niitä ehkäistään nykyaikaisessa piirilevyvalmistuksessa.

Sisällysluettelo

Mikä on PCB-virhe?

Piirilevyn vikaantuminen tapahtuu, kun levy ei enää täytä sen vaatimuksia. sähköiset, mekaaniset tai luotettavuutta koskevat vaatimukset.

Epäonnistumisia voi esiintyä:

- Sähköisen testauksen aikana

- PCB-kokoonpanon aikana

- Lämpökierron jälkeen

- Todellisessa käytössä

Monet viat syntyvät jo kauan ennen kuin piirilevylle kytketään virta.

Avoimet piirit ja oikosulut

Tyypilliset oireet

- Sähkötestin epäonnistuminen

- Ei signaalin jatkuvuutta

- Odottamattomat virran kulkureitit

Yleiset syyt

- Epätäydellinen kuparointi

- Yli- tai alietsaus

- Sisäkerroksen virheellinen rekisteröinti

Ehkäisymenetelmät

- Valvotut etsausprosessit

- Sähköinen testaus (E-testi)

- AOI-tarkastus valmistuksen aikana

Liittyy asiaan: PCB:n sähköinen testaus selitetty

Delaminaatio

Delaminaatiolla tarkoitetaan piirilevykerrosten tai kuparin ja dielektrisen materiaalin välistä erottelua.

Oireet

- Rakkuloituminen juottamisen aikana

- Röntgenkuvassa näkyvät sisäiset tyhjät tilat

- Vähentynyt mekaaninen lujuus

Juurisyyt

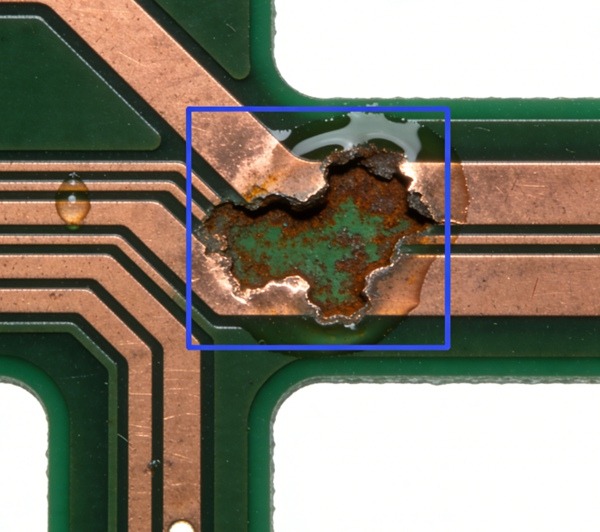

- Liiallinen kosteuden imeytyminen

- Virheelliset laminointiparametrit

- Yhteensopimattoman materiaalin valinta

Syvällinen opas:

PCB Delamination Syyt ja ehkäisy

Delaminaatio

Delaminaatiolla tarkoitetaan piirilevykerrosten tai kuparin ja dielektrisen materiaalin välistä erottelua.

Oireet

- Rakkuloituminen juottamisen aikana

- Röntgenkuvassa näkyvät sisäiset tyhjät tilat

- Vähentynyt mekaaninen lujuus

Juurisyyt

- Liiallinen kosteuden imeytyminen

- Virheelliset laminointiparametrit

- Yhteensopimattoman materiaalin valinta

Syvällinen opas:

PCB Delamination Syyt ja ehkäisy

Johtavan anodisen filamentin (CAF) viat

CAF on piilevä vikatila, joka kehittyy ajan myötä.

Ominaisuudet

- Asteittainen eristyksen hajoaminen

- Ilmaantuu usein kuukausien tai vuosien kuluttua

- Kosteuden ja jännitteen aiheuttama poikkeama laukaisee sen.

Myötävaikuttavat tekijät

- Lasikuidulle altistuminen

- Hartsirikkaat alueet

- Korkean kosteuden ympäristöt

Tekninen erittely:

CAF:n epäonnistuminen PCB:ssä selitetty

Juotosnaamion ja pintaan liittyvät viat

Vaikka pintaan liittyvät viat jäävät usein huomaamatta, ne voivat aiheuttaa todellisia toiminnallisia ongelmia.

Esimerkkejä

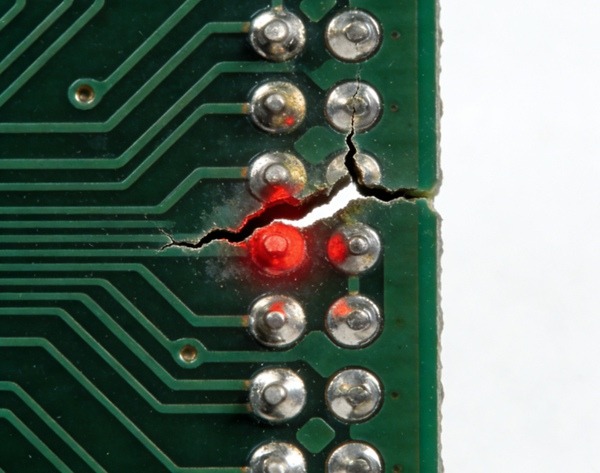

- Juotosmaskin halkeilu

- Huono tarttuvuus

- Korroosioaltistus

Ennaltaehkäisy

- Asianmukainen pinnan valmistelu

- Valvotut kovettumisprosessit

- Materiaalien yhteensopivuuden tarkastukset

Miten PCB-virheanalyysi suoritetaan

Kun vikoja ilmenee, valmistajat käyttävät strukturoituja analyysimenetelmiä.

Yleisiä työkaluja ovat:

- Poikkileikkausanalyysi

- Röntgentarkastus

- Lämpökuormitustestaus

- Sähköinen uudelleentestaus

Menetelmien yleiskatsaus:

PCB-virheanalyysimenetelmät selitetty

Tuotantoprosessin valvonnan rooli

Useimmat PCB-viat ovat estettävissä.

Keskeisiä valvonta-alueita ovat:

- Laminointiprofiilit

- Kuparipinnoituksen paksuus

- Materiaalin varastointi ja käsittely

- Tarkastusten ja testien kattavuus

TOPFASTin kaltaiset valmistajat sisällyttävät vikapalautteen jatkuvaan prosessin parantamiseen sen sijaan, että käsittelisivät vikoja yksittäisinä tapahtumina.

Vikaantumisriskiä lisäävät suunnittelupäätökset

Suunnitteluvalinnat vaikuttavat voimakkaasti vikaantumistodennäköisyyteen.

Suuren riskin suunnittelukäytäntöjä ovat muun muassa:

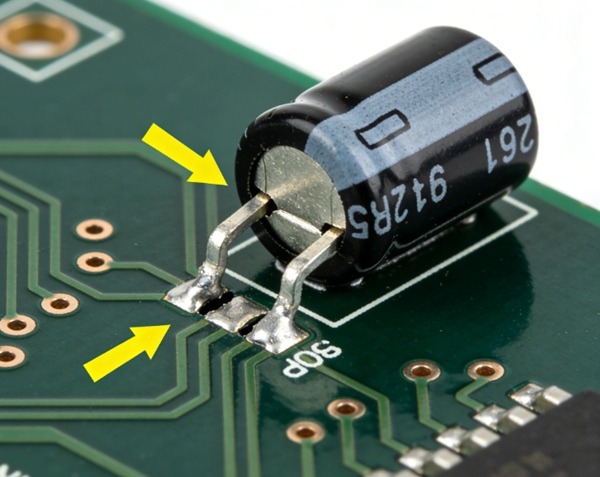

- Erittäin ohuet dielektriset aineet

- Minimaaliset rengasrenkaat

- Suuren kuvasuhteen läpiviennit

- Tiiviit välit kosteissa ympäristöissä

Suunnittelun näkökulma:

PCB-laadun ja luotettavuuden suunnitteluohjeet

Päätelmä

Piirilevyviat johtuvat harvoin yhdestä ainoasta tekijästä.

Ne ovat yleensä seurausta suunnittelun, materiaalien ja valmistusprosessien väliset vuorovaikutussuhteet..

Yleisten vikaantumistapojen ymmärtämisen avulla insinöörit voivat:

- Suunnittele vankempia piirilevyjä

- Sopivien materiaalien valinta

- Oikeiden tarkastus- ja testausstrategioiden soveltaminen

Tämä artikkeli toimii perustana PCB-virheanalyysi sisällön klusteri.

Yleiset PCB-viat FAQ

V: Useimmissa epäonnistumisissa on kyse molemmista.

V: Ei. Tarkastus vähentää riskiä, mutta sillä ei voida ennustaa pitkäaikaista heikkenemistä.

V: CAF- ja via-säröt ovat usein piileviä ja vaativat rasitustestausta.

V: Ei. Prosessinhallinta on tärkeämpää kuin pelkät kustannukset.

V: Kun viat ovat ajoittaisia, toistuvia tai kenttään liittyviä.