Tekoälyn ja suurnopeussovellusten perusteista kehittyneisiin strategioihin

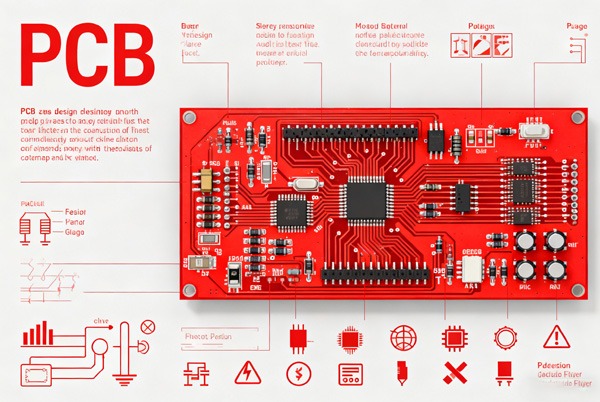

Painettu piirilevy on elektroniikkatuotteiden luuranko ja hermosto. Kaiken yksinkertaisista mikrokontrolleriprojekteista monimutkaisiin tekoälypalvelimiin ulottuvan toiminnan vakaus ja suorituskyky ovat vahvasti riippuvaisia piirilevysuunnittelun laadusta. Tämä opas, jonka on koonnut insinööritiimin asiantuntijatiimi TOPFASTtarjoaa täydellisen etenemissuunnitelman peruskäsitteistä edistyneisiin strategioihin.

Sisällysluettelo

Perustava PCB-suunnitteluprosessi - vankka lähtökohta

Aloittelijoille standardoidun suunnitteluprosessin noudattaminen on avain menestykseen.

1: Suunnittelun valmistelu - kaavio ja sääntöjen määrittely

- Luonnossuunnittelu: Tämä on looginen perusta. Varmista, että symbolit ovat oikein, liitännät ovat tarkkoja ja että jokaiselle komponentille on määritetty oikea jalanjälki.

- Ennen ulkoasun suunnittelua: Varhainen yhteydenpito PCB-valmistaja (kuten TOPFAST) on ratkaisevan tärkeää. Hanki heidän Prosessin kyvykkyysasiakirja, määrittelemällä parametrit, kuten minimijäljen leveys/väli, minimireikäkoko, pinoamisrakenne, ja asettamalla nämä suunnittelusäännöiksi DFM-ongelmien välttämiseksi alusta alkaen.

2: Komponenttien sijoittelu - sähköisen järjestelmän "kaupunkisuunnittelu".

- Keskeinen periaate: "Sijainti on kaikki kaikessa."

- Kriittiset komponentit ensin: Aseta pääohjain (CPU/FPGA), muisti ja virranhallintapiirit ensin.

- Toiminnallinen modularisointi: Ryhmittele toisiinsa liittyvät piirit yhteen (esim. virtalähde, kellopiiri, analoginen osa).

- Huomioi lämpö- ja kokoonpano: Jaa suuritehoiset komponentit ja suunnittele lämpöreitit; sijoita liittimet ja kytkimet ottaen huomioon kotelomekaniikka ja käyttäjäkokemus.

3: Reititys - Yhteyksien taito ja tiede

- Teho ensin: Reititä virta- ja maajohdot aikaisin ja varmista, että ne ovat lyhyitä ja leveitä impedanssin minimoimiseksi.

- Kriittiset signaalit Prioriteetti: Reititä kellot, nopeat differentiaaliparit ja herkät analogiset signaalit lyhimmillä ja puhtaimmilla reiteillä.

- 3W-sääntö: Säilytä rinnakkaisten jälkien väli vähintään 3 kertaa jäljen leveyden verran ristikkäisviestinnän vähentämiseksi.

- Maadoitusstrategia: Käytä tyypillisesti jaettua maatasoa digitaalisille ja analogisille osille, jotka on kytketty yhteen pisteeseen häiriöiden välttämiseksi.

4: Jälkikäsittely ja valmistustiedoston tuottaminen

- DRC Check: Suorita lopullinen suunnittelusääntöjen tarkistus sen varmistamiseksi, että mitään ei ole jätetty huomiotta.

- Gerber- ja poratiedostojen luominen: Nämä ovat valmistuksen vakiotiedostoja. Lisäksi tulostetaan IPC-356-verkkoluettelo levyn lentävän koettimen testausta varten, jotta voidaan varmistaa, että sähköinen liitettävyys vastaa suunnittelua.

- Kommunikoi valmistajan kanssa: Tarjota selkeä Kokoonpanopiirustus ja Prosessivaatimukset (esim. pintakäsittely - Immersion Gold, HASLvai ENIG?). Tämä parantaa viestintää ja varmistaa, että ammattimainen kumppani kuten TOPFAST ymmärtää tarkasti "Design for Manufacture" -tarpeesi.

TOPFAST-vinkki: Alkuvaiheen prototyyppejä varten suositellaan vahvasti Sähkötesti (E-testi) ja Lentävän koettimen testi. Tämä on viimeinen, kustannustehokkain puolustuslinja mahdollisia oikosulkuja tai aukkoja vastaan.

Edistyneet käytännöt - suunnittelufilosofia tekoälyä ja nopeiden skenaarioiden suunnittelua varten

Kun suunnittelusi siirtyy GHz-aikaan tekoälykiihdytinkorttien tai nopeiden kytkimien osalta, perussäännöt ovat vain lähtökohta. Onnistuminen riippuu yhteissuunnittelusta eheys ja valmistettavuus.

1. Paradigman muutos: Järjestelmän yhteissuunnittelusta "järjestelmän yhteissuunnitteluun".

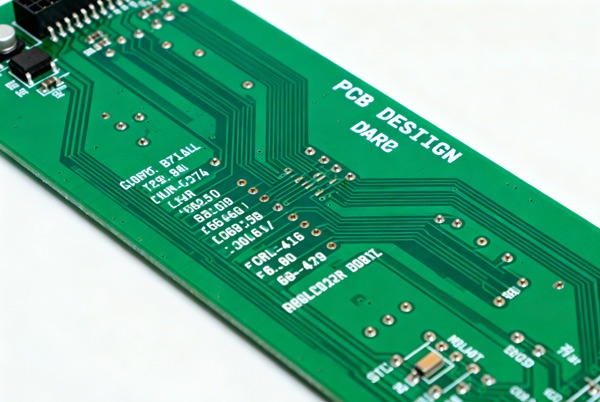

Nykyaikainen nopea piirilevy on 3D-kompleksi, joka koostuu seuraavista osista signaalinsiirtolinjat, a monimutkainen sähkönjakeluverkko (PDN)ja tarkka lämmönhallintajärjestelmä. Tavoite siirtyy "toiminnallisuuden saavuttamisesta" seuraavien tekijöiden välisen tasapainon optimoimiseen. Signaalin eheys (SI), virran eheys (PI) ja lämmön eheys (Thermal Integrity)..

2. Kriittinen perusta: DFM ja luotettavuussuunnittelu yhteistyössä TOPFASTin kanssa.

- Tarkka impedanssin säätö: Kyse ei ole vain jäljen leveyden laskemisesta. Vahvista erityinen ydin/prepreg-materiaalit valmistajan kanssa. TOPFASTin insinööritiimi tarjoaa neuvontapalvelut ja impedanssin laskentapalvelut stack-upin osalta varmistaa johdonmukaisuus suunnittelusta valmiiseen tuotteeseen.

- Kehittynyt Via-suunnittelu ja takaporaus: Sokeat ja haudatut viat ovat välttämättömiä tiheille BGA-levyille. Yli 10 Gbps:n signaaleja varten, Takaisinporaus (Stub Removal) on vakiomenetelmä, jolla poistetaan tynkävaikutukset ja varmistetaan signaalin eheys. Vahvista valmiudet tällaisiin kehittyneisiin prosesseihin TOPFAST suunnitteluvaiheessa.

3. Simulointipohjainen suunnittelu: "Prototyyppien luominen virtuaalimaailmassa

Vanha "suunnittelu-tuotanto-testi-muutos"-sykli on kallis ja hidas. Nykyaikaisen työnkulun tulisi olla iteratiivinen. "simulate-optimize-resimulate" prosessi.

- SI/PI-yhteissimulointi: Analysoidaan koko PDN:n impedanssi. Optimoi kytkentäkondensaattorin sijoittelu, jotta varmistetaan erittäin alhainen impedanssi sirun virtanastoilla.

- 3D-sähkömagneettinen (EM) simulointi: Käytä 3D-täysaaltoratkaisuja monimutkaisten liittimien ja läpivientien käyttäytymisen tarkkaan mallintamiseen laajoilla taajuusalueilla.

TOPFAST-tapaustutkimus: Erään asiakkaan tekoälykiihdytinkorttihankkeessa ensimmäinen prototyyppi osoitti korkeaa bittivirheprosenttia (BER) 25 Gbps:n nopeudella. Yhdistetyn kanavasimulointi ja TOPFASTin PCB-prosessianalyysitodettiin, että tietyn laminaatin dielektrinen häviö (Df) oli odotettua suurempi. Kun TOPFASTin suositus, materiaali vaihdettiin M7NE, erittäin matalahäviöinen materiaali, ja lasin kudontatyyli optimoitiin. Tämä mahdollisti vakaan toiminnan 32 Gbps:n nopeudella ja BER-arvon ollessa parempi kuin 1E-12 ilman suunnittelumuutoksia.

4. Tulevaisuuden suunnittelu: Yhteistyö asiantuntijoiden kanssa huipputekniikan kehittämiseksi.

Teknologian eturintama etenee jatkuvasti. Seuraavan sukupolven järjestelmiin valmistautuminen edellyttää seuraavien asioiden huomioimista:

- Erittäin alhaisen häviön materiaalit: Kun tiedonsiirtonopeudet lähestyvät 112 Gbps PAM-4:ää, tavallinen FR-4 ei enää kestä häviöiden vuoksi.

- Järjestelmätason yhteissuunnittelu: Mallinna ja analysoi piirilevy, liittimet ja kaapelit yhtenä järjestelmänä.

- Syvällinen yhteistyö TOPFASTin kaltaisen kumppanin kanssa: Kokenut valmistuskumppani ei tarjoa vain tuotteita, vaan kokenut valmistuskumppani tarjoaa kokeneen valmistuskumppanin, joka tarjoaa aina kokoonpanokonsultoinnista ja DFM-katselmuksesta erikoisprosessien toteuttamiseen (esim. hybridi-press-sovitus, jäykkä-jousto). jatkuva tekninen ymmärrys ja varmuus koko matkan ajan.

Päätelmä

Piirilevysuunnittelu on huolellinen matka logiikasta fysiikkaan, virtuaalisesta todellisuuteen. Poikkeukselliset insinöörit ovat sekä tiedemiehiä, jotka hallitsevat virtapiirit ja sähkömagneettiset kentät, että ammattilaisia, jotka ymmärtävät syvällisesti materiaaleja ja prosesseja. Yhteistyö TOPFASTin kaltaisen ammattimaisen valmistajan kanssa tarkoittaa, että sinulla on insinööriliittolainen mukana koko matkan ajan suunnittelusta massatuotantoon. Näin varmistetaan, että ideasi, olivatpa ne sitten perustavanlaatuisia tai huippuluokan ideoita, muunnetaan vakaiksi ja luotettaviksi tuotteiksi, jotka ovat korkealaatuisia ja nopeatempoisia ja jotka varmistavat kilpailuetusi markkinoilla.

PCB Design FAQ

A:Oire: Vaikka impedanssi lasketaan suunnittelun aikana, valmis levy ei täytä tavoitearvoja tai siinä on epäjatkuvuuksia. Tämä aiheuttaa signaalien heijastumista, silmäkaavion sulkeutumista ja järjestelmän epävakautta erityisesti nopeissa signaaleissa (esim. HDMI, USB3.0, PCIe).

Juurisyy:

Suunniteltu pinoamisrakenne ei vastaa materiaaleja valmistajan tosiasiallisesti käyttämä (esim. poikkeamat ytimen/prepreg-tyypin tai dielektrisyysvakion (Dk) suhteen).

Jäljen leveys tai dielektrinen paksuus vaihtelee valmistustoleranssien vuoksi.

Epätäydellinen vertailutaso; signaalijäljet kulkevat tasossa olevien halkaisijoiden (anti-pads) yli.

Ratkaisu:

Ota yhteyttä valmistajasi (kuten TOPFAST) kanssa varhaisessa vaiheessa: Hanki ja käytä valmistajan suosittelemaa pinoamispöytä ja impedanssin laskentaparametrit ennen asettelua.

Selkeä huomautus: Merkitse selvästi, mitkä jäljet ovat ohjattu impedanssi, niiden tavoitearvo ja viitekerros Gerber-tiedostoissa ja valmistusmuistiinpanoissa.

Vältä risteyksiä: Varmista, että suurnopeussignaalijäljitelmien alla on kiinteä, jatkuva vertailutaso.

A:Oire: Merkittävä jännitteen aaltoilu piirin virtanastoissa, mikä johtaa satunnaisiin järjestelmävirheisiin erityisesti nopeiden logiikkakytkentöjen aikana.

Juurisyy:

Liian kauas sirun virtanastoista sijoitetut purkauskondensaattorit, jotka aiheuttavat liiallisen loisinduktanssin, tekevät niistä tehottomia korkeilla taajuuksilla.

Sopimattomien kondensaattorien arvojen tai tyyppien käyttö (esim. sellaisten pienikokoisten kondensaattorien puuttuminen, joilla on hyvät korkeataajuusominaisuudet).

Itse tehopolku on liian ohut tai pitkä, ja siinä on korkea impedanssi.

Ratkaisu:

"Läheisyysperiaate": Sijoita pienikokoiset kondensaattorit (esim. 0,1 µF, 0,01 µF) mahdollisimman lähelle piirin virtanastoja ja etusijalle lyhin paluureitti.

Optimoi viat: Käytä useita läpivientejä virta-/maaliitäntöihin induktanssin vähentämiseksi.

Suorita PDN-analyysi: Validoi kytkennästä irrottamisstrategia käyttämällä Power Integrity (PI) -simulaatioita sen sijaan, että tukeudut pelkkään kokemukseen.

A:Oire: Kyvyttömyys reitittää kaikkia signaaleja suurikokoisista BGA-piireistä (esim. FPGA:t, GPU:t) tai pakko lisätä useita piirilevykerroksia vain tuulettimen ulosottoa varten, mikä lisää kustannuksia merkittävästi.

Juurisyy:

Kaikkien käytettävissä olevien reitityskanavien hyödyntämättä jättäminen BGA:n alla. Luottaminen vain perinteiseen "koiranluu"-tyynyn tuuletukseen.

Tuntemattomuus valmistajan microvia-ominaisuuksien suhteen, mikä johtaa sokean/haudatun läpivientitekniikan välttämiseen.

Ratkaisu:

Käytä VIP-tekniikkaa (Via-in-Pad): Aseta laserporatut mikroviat suoraan BGA-tyynyihin. Tämä on suositeltavin menetelmä tiheässä BGA-suunnittelussa.

Konsultoi valmistuskapasiteettia: Vahvista laserporauksen tarkkuus ja pinottu valmiuksien kautta TOPFASTin kanssa. Suunnittele HDI (High-Density Interconnect) (tiheä liitäntä) ja sokeat/hautetut läpiviennit suunnitteluvaiheen alkuvaiheessa, jolloin voidaan usein saavuttaa suurempi reititystiheys vähemmillä kerroksilla.

A:Oire: Suuritehoiset komponentit (esim. prosessorit, teho-IC:t) ylikuumenevat kuormituksessa, jolloin lämpösuojaus käynnistyy ja aiheuttaa suorituskyvyn hidastumisen tai järjestelmän nollautumisen.

Juurisyy:

PCB-lämpösuunnittelu jätetään huomiotta. Luotetaan pelkästään komponentin jäähdytyselementtiin johtamatta lämpöä tehokkaasti levylle tai koteloon.

Sirun alla ei ole riittävästi kuparia lämmön tehokkaaseen leviämiseen.

Lämpöläpivientien puuttuminen tai niiden puutteellinen täyttäminen.

Ratkaisu:

Lisää lämpöpolkuja: Aseta tiheä joukko termisesti täytetyt läpiviennit piirilevyn maadoituskuviossa sirun alla, jotta lämpö siirtyy nopeasti vastakkaisella puolella olevaan maadoitus-/virtatasoon.

Lisää kuparialuetta: Varaa suuremmat kuparialueet sisäisille tasoille (erityisesti maadoitetuille) lämmityskomponenttien alapuolelle lämmöntuottamisen helpottamiseksi.

Käytä paksumpaa kuparifoliota: Suuren virran/korkean kuumuuden alueilla, kysy TOPFASTin neuvoa, miten käyttää raskaat kuparifoliot (esim. 2oz).

A:Oire: Suunnittelu toimii täydellisesti simuloinnissa/prototyypissä, mutta piensarjatuotanto kärsii alhaisesta tuotosta, tai SMT-kokoonpanon aikana ilmenee ongelmia, kuten tombstoning, juotosillat tai kylmät liitokset.

Juurisyy:

Perusvaatimusten noudattamatta jättäminen Valmistettavuuden suunnittelu (DFM) ja Kokoonpanosuunnittelu (DFA) säännöt.

Komponenttien huono sijoittelu (esim. hienojakoisten QFP-korttien sijoittaminen aaltojuotospuolelle).

Vääränlainen kaavion aukon muotoilu.

Ratkaisu:

Kunnioita prosessikykyä: Varmista, että alustojen etäisyys ja komponenttien etäisyys toisistaan ovat SMT-laitteiden vaatimusten mukaiset. Vältä herkkien/pienten komponenttien sijoittamista suurempien osien varjoon uudelleenjuoksutuksen aikana tai aaltojuotosalueilla.

Tarkan Centroid-tiedoston toimittaminen: Luo oikea pick-and-place-tiedosto (keskipistetiedosto), joka sisältää viitetunnisteen, X/Y-koordinaatit ja pyörimisen, mikä varmistaa koneen tarkan ohjelmoinnin.

Hyödynnä valmistajan DFM-tarkistus: Toimita suunnittelutiedostot TOPFASTille ammattimainen DFM-analyysi ennen tuotantoa. Näin voidaan tunnistaa mahdolliset ongelmat, kuten huono tyynyn suunnittelu, happolukot tai riittämätön kokoonpanoväli, varhaisessa vaiheessa, jolloin vältetään kalliit uudelleenkierrokset.