Van grondbeginselen tot geavanceerde strategieën voor AI en snelle toepassingen

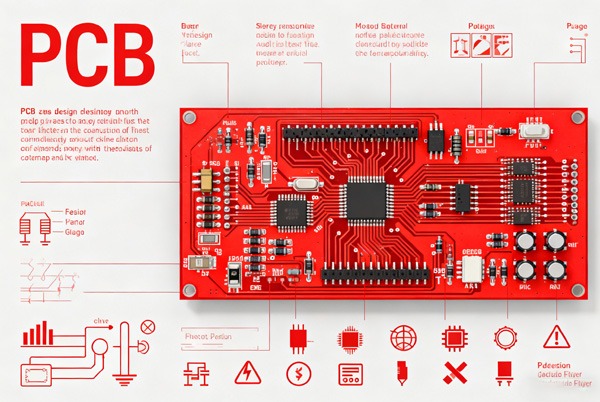

De printplaat is het skelet en het zenuwstelsel van elektronische producten. De stabiliteit en prestaties van alles, van eenvoudige microcontrollerprojecten tot complexe AI-servers, zijn diep geworteld in de kwaliteit van het PCB-ontwerp. Deze gids, samengesteld door het technische expertteam van TOPFASTbiedt een compleet stappenplan van basisconcepten tot geavanceerde strategieën.

Inhoudsopgave

Fundamenteel PCB-ontwerpproces - Een robuust uitgangspunt

Voor beginners is het volgen van een gestandaardiseerd ontwerpproces de sleutel tot succes.

1: Ontwerpvoorbereiding - Schema en regeldefinitie

- Schematisch ontwerp: Dit is de logische basis. Zorg ervoor dat de symbolen kloppen, dat de verbindingen correct zijn en wijs de juiste voetafdruk toe aan elk onderdeel.

- Pre-layout planning: Vroege communicatie met uw PCB-fabrikant (zoals TOPFAST) is cruciaal. Verkrijg hun Document met procesmogelijkhedenDefinieer parameters zoals minimale spoorbreedte/-spacing, minimale gatgrootte, stapelstructuur en stel deze in als ontwerpregels om DFM-problemen vanaf het begin te voorkomen.

2: Plaatsing van componenten - de "stedenbouw" van een elektronisch systeem

- Kernprincipe: "Locatie is alles."

- Kritieke onderdelen eerst: Plaats de hoofdcontroller (CPU/FPGA), het geheugen en de energiebeheer-IC's eerst.

- Functionele modularisatie: Groepeer verwante circuits (bijv. voeding, klokcircuit, analoog gedeelte).

- Denk aan thermische en assemblage: Componenten met hoog vermogen verdelen en thermische paden plannen; connectoren en schakelaars plaatsen rekening houdend met de mechanica van de behuizing en de gebruikerservaring.

3: Routing - de kunst en wetenschap van verbinding

- Macht eerst: Leg de voedings- en massasporen vroeg en zorg ervoor dat ze kort en breed zijn om impedantie te minimaliseren.

- Kritieke signalen Prioriteit: Routeer klokken, differentiële paren met hoge snelheid en gevoelige analoge signalen met de kortste, zuiverste paden.

- 3W-regel: Zorg voor een parallelle spoorafstand van minstens 3 keer de spoorbreedte om overspraak te beperken.

- Aardingsstrategie: Gebruik meestal een gesplitste massaplaat voor digitale en analoge secties, aangesloten op een enkel punt om ruisinterferentie te voorkomen.

4: Nabewerking en genereren van productiebestanden

- DRC-check: Voer een laatste ontwerpregelcontrole uit om er zeker van te zijn dat er geen fouten zijn gemaakt.

- Gerber- en boorbestanden genereren: Dit zijn de standaardbestanden voor productie. Voer ook een IPC-356 netlijst voor tests met een vliegende sonde op de printplaat om te controleren of de elektrische connectiviteit overeenkomt met het ontwerp.

- Communiceer met de fabrikant: Zorg voor een duidelijke Montage tekening en Procesvereisten (bijv. oppervlakteafwerking - Immersion Gold, HASLof ENIG?). Dit verbetert de communicatie en zorgt voor een professionele partner zoals TOPFAST begrijpt nauwkeurig uw behoeften voor "Design for Manufacture".

TOPFAST Tip: Voor eerste prototypen raden we ten zeerste aan Elektrische test (E-test) en Test met vliegende sonde. Dit is de laatste, meest kosteneffectieve verdedigingslinie tegen potentiële kortsluitingen of openingen.

Geavanceerde praktijken - Ontwerpfilosofie voor AI en hogesnelheidsscenario's

Wanneer je ontwerp het GHz-tijdperk betreedt voor AI-acceleratiekaarten of hogesnelheidsschakelaars, zijn de basisregels slechts het uitgangspunt. Succes hangt af van het co-ontwerp van integriteit en maakbaarheid.

1. Paradigmaverschuiving: Van "interconnectie" naar "systeem co-ontwerp".

Een moderne PCB met hoge snelheid is een 3D-complex dat bestaat uit lijnen voor signaaloverdracht, a complex stroomdistributienetwerk (PDN)en een nauwkeurig systeem voor thermisch beheer. Het doel verschuift van "functionaliteit bereiken" naar het optimaliseren van de balans tussen Signaalintegriteit (SI), vermogensintegriteit (PI) en thermische integriteit.

2. De kritische basis: DFM en Betrouwbaarheidsontwerp in samenwerking met TOPFAST

- Nauwkeurige impedantieregeling: Het gaat niet alleen om berekeningen van de spoorbreedte. Bevestig de specifieke kern/prepreg-materialen met je fabrikant. TOPFAST's engineeringteam biedt adviesdiensten voor stapeling en impedantieberekening om consistentie van ontwerp tot eindproduct te garanderen.

- Geavanceerd Via-ontwerp en terugboren: Blinde en begraven Vias zijn essentieel voor BGA's met hoge dichtheid. Voor signalen van meer dan 10 Gbps, Terugboren (Stub Removal) is een standaardproces om stubeffecten te elimineren en signaalintegriteit te garanderen. Mogelijkheden voor dergelijke geavanceerde processen bevestigen met TOPFAST tijdens de ontwerpfase.

3. Simulatiegestuurd ontwerpen: "Prototyping" in de virtuele wereld

De oude cyclus "ontwerpen-fabriceren-testen-herzien" is duur en traag. De moderne workflow moet een iteratieve "simuleren-optimaliseren-resimuleren". proces.

- SI/PI Co-Simulatie: De impedantie van het hele PDN analyseren. Optimaliseer de plaatsing van ontkoppelingscondensatoren om een extreem lage impedantie op de voedingspennen van de chip te garanderen.

- 3D elektromagnetische (EM) simulatie: Gebruik 3D full-wave solvers om het gedrag van complexe connectoren en vias over een breed frequentiebereik nauwkeurig te modelleren.

Casestudie TOPFAST: In het AI-acceleratorkaartproject van een klant vertoonde het eerste prototype een hoge Bit Error Rate (BER) bij 25 Gbps. Door gecombineerde kanaalsimulatie en PCB-procesanalyse van TOPFASTwerd vastgesteld dat het diëlektrisch verlies (Df) van een specifiek laminaat hoger was dan verwacht. Op TOPFAST's aanbeveling werd het materiaal overgeschakeld op M7NE, een materiaal met ultralaag verlies, en de glasweefstijl werd geoptimaliseerd. Dit zorgde voor een stabiele werking bij 32 Gbps met een BER beter dan 1E-12, zonder enige veranderingen aan het ontwerp.

4. Ontwerpen voor de toekomst: Samenwerken met experts voor geavanceerde technologie

De technologische grens gaat altijd verder. Voorbereiding op systemen van de volgende generatie vereist aandacht voor:

- Materialen met ultralaag verlies: Wanneer de gegevenssnelheden 112 Gbps PAM-4 naderen, wordt standaard FR-4 onhoudbaar vanwege verlies.

- Co-ontwerp op systeemniveau: Modelleer en analyseer de printplaat, connectoren en kabels als één systeem.

- Diepgaande samenwerking met een partner als TOPFAST: Van advies over stapelconfiguraties en DFM-evaluatie halverwege de cyclus tot het implementeren van gespecialiseerde processen (bijv. hybride press-fit, rigid-flex), een ervaren productiepartner levert niet alleen producten, maar ook continu technisch inzicht en zekerheid tijdens de hele reis.

Conclusie

PCB-ontwerp is een nauwgezette reis van logica naar fysica, van virtueel naar realiteit. Uitzonderlijke ingenieurs zijn zowel wetenschappers die circuits en elektromagnetische velden beheersen, als praktijkmensen die materialen en processen door en door begrijpen. Samenwerken met een professionele fabrikant als TOPFAST betekent dat er een technische bondgenoot aanwezig is tijdens uw hele reis, van ontwerp tot massaproductie. Dit zorgt ervoor dat uw ideeën, of ze nu fundamenteel of baanbrekend zijn, worden omgezet in stabiele, betrouwbare producten met de hoogste kwaliteit en de hoogste snelheid, waardoor uw concurrentievoordeel op de markt wordt veiliggesteld.

PCB-ontwerp FAQ

A:Symptoom: Tijdens het ontwerp wordt de impedantie berekend, maar het afgewerkte bord voldoet niet aan de doelwaarden of vertoont discontinuïteiten. Dit veroorzaakt signaalreflectie, het sluiten van oogdiagrammen en instabiliteit van het systeem, vooral bij signalen met hoge snelheid (bijvoorbeeld HDMI, USB3.0, PCIe).

Oorzaak:

De ontworpen stapelstructuur komt niet overeen met de materialen die daadwerkelijk door de fabrikant zijn gebruikt (bijv. discrepanties in kern/prepreg type of Diëlektrische constante - Dk).

De spoorbreedte of diëlektrische dikte varieert door fabricagetoleranties.

Onvolledig referentievlak; signaalsporen lopen over splitsingen (anti-pads) in het vlak.

Oplossing:

Neem vroeg contact op met uw fabrikant (zoals TOPFAST): Verkrijg en gebruik de door de fabrikant aanbevolen stapeltabel en impedantieberekeningsparameters voor de layout.

Duidelijke annotatie: Markeer duidelijk welke sporen gecontroleerde impedantiehun doelwaarde en referentielaag op de Gerber-bestanden en fabricageopmerkingen.

Vermijd kruisingen: Zorg ervoor dat signaalsporen met hoge snelheid een stevig, ononderbroken referentievlak eronder hebben.

A:Symptoom: Aanzienlijke spanningsrimpel op de voedingspinnen van de chip, wat leidt tot willekeurige systeemfouten, vooral tijdens het schakelen van logica met hoge snelheid.

Oorzaak:

Ontkoppelcondensatoren die te ver van de voedingspennen van de chip geplaatst zijn en een te grote parasitaire inductie introduceren, maken ze ineffectief bij hoge frequenties.

Gebruik van ongeschikte condensatorwaarden of -types (bijv. geen condensatoren van kleine waarde met goede hoogfrequente eigenschappen).

Het stroompad zelf is te dun of te lang, waardoor het een hoge impedantie heeft.

Oplossing:

"Nabijheidsprincipe: Plaats condensatoren met een kleine waarde (bijv. 0,1µF, 0,01µF) zo dicht mogelijk bij de voedingspinnen van de chip en geef daarbij prioriteit aan het kortste retourpad.

Vias optimaliseren: Gebruik meerdere vias voor voedings-/massaverbindingen om inductantie te verminderen.

PDN-analyse uitvoeren: Valideer de ontkoppelingsstrategie met behulp van Power Integrity (PI)-simulaties in plaats van alleen op ervaring te vertrouwen.

A:Symptoom: Het onvermogen om alle signalen van BGA-chips met een hoog aantal pinnen (bv. FPGA's, GPU's) te routeren of gedwongen worden om veel PCB-lagen toe te voegen voor fan-out, wat de kosten aanzienlijk verhoogt.

Oorzaak:

Het niet gebruiken van alle beschikbare routingkanalen onder de BGA. Alleen vertrouwen op de traditionele "dog-bone" pad fan-out.

Onbekendheid met de microvia mogelijkheden van de fabrikant, wat leidt tot het vermijden van blinde of ingegraven via technologie.

Oplossing:

Gebruik Via-in-Pad (VIP)-technologie: Plaats lasergeboorde microvia's rechtstreeks in de BGA-pads. Dit is de voorkeursmethode voor BGA-ontwerp met hoge dichtheid.

Productiemogelijkheden raadplegen: Bevestig precisie laserboren en gestapeld via mogelijkheden met TOPFAST. Plan voor HDI (High-Density Interconnect) en blinde/ingegraven vias vroeg in de ontwerpfase, waardoor vaak een hogere freesdichtheid kan worden bereikt met minder lagen.

A:Symptoom: Krachtige componenten (zoals processors en voedings-IC's) raken oververhit onder belasting, waardoor de thermische beveiliging in werking treedt en de prestaties afnemen of het systeem gereset wordt.

Oorzaak:

Het thermisch ontwerp van PCB's wordt verwaarloosd. Er wordt enkel vertrouwd op het koellichaam van de component zonder dat de warmte effectief wordt afgevoerd naar de printplaat of de behuizing.

Onvoldoende koperoppervlak onder de chip voor effectieve warmteverspreiding.

Gebrek aan thermische doorvoeringen of ze zijn onvoldoende gevuld.

Oplossing:

Thermische paden toevoegen: Plaats een dichte matrix van thermisch gevulde doorvoeropeningen in het PCB-landpatroon onder de chip om warmte snel af te voeren naar het massa-/vermogenvlak aan de andere kant.

Koperoppervlak vergroten: Wijs grotere koperen oppervlakken toe op interne vlakken (vooral aarde) onder verwarmingscomponenten om de warmteafvoer te bevorderen.

Gebruik dikkere koperfolie: Raadpleeg TOPFAST voor gebieden met hoge stroomsterkte en hitte over het gebruik van zware koperfolie (bijv. 2oz).

A:Symptoom: Het ontwerp werkt perfect in simulatie/prototype, maar de productie in kleine series heeft te kampen met een lage opbrengst, of er treden problemen op zoals tombstoning, soldeerbruggen of koude verbindingen tijdens SMT-assemblage.

Oorzaak:

Het niet naleven van de basis Ontwerp voor maakbaarheid (DFM) en Ontwerp voor assemblage (DFA) regels.

Slechte plaatsing van componenten (bijvoorbeeld het plaatsen van QFP's met een fijne pitch aan de golfsoldeerkant).

Verkeerd ontwerp van de sjabloonopening.

Oplossing:

Respecteer procesmogelijkheden: Zorg ervoor dat de padafstand en componentafstand voldoen aan de vereisten van SMT-apparatuur. Plaats gevoelige/kleine onderdelen niet in de schaduw van grotere onderdelen tijdens reflow of in golfsoldeerzones.

Zorg voor een nauwkeurig centroïdebestand: Een correcte pick-and-place bestand (centroïdebestand) met referentieaanduiding, X/Y-coördinaten en rotatie, zodat de machine nauwkeurig geprogrammeerd kan worden.

Maak gebruik van de DFM-check van de fabrikant: Ontwerpbestanden naar TOPFAST sturen voor een professionele DFM-analyse voor de productie. Hierdoor kunnen potentiële problemen zoals een slecht padontwerp, zuurvallen of onvoldoende assemblagespeling vroegtijdig worden geïdentificeerd, waardoor kostbare re-spins worden voorkomen.