Hoe impedantieregeling voor PCB ontwerpen?

Inhoudsopgave

Het belang van PCB-impedantieregeling

In de hedendaagse snelle elektronische apparaten worden de snelheden van signaaloverdracht steeds hoger en is PCB impedantiecontrole een belangrijke factor geworden bij het bepalen van het succes of falen van een ontwerp. Een verkeerde impedantie kan signaalreflectie, ringing en overshootproblemen veroorzaken, die de signaalintegriteit ernstig aantasten. Volgens statistieken is meer dan 60% van de storingen in digitale hogesnelheidsschakelingen te wijten aan onjuiste impedantieregeling. Daarom is het essentieel om de PCB impedantiecontroletechnologie onder de knie te krijgen.

De vier pijlers van impedantieregeling

1. Materiaalkeuze

“Kies het juiste materiaal en je’ bent al halverwege je succes”-Dit geldt vooral voor impedantieregeling:

- Aanbevolen hoogfrequent materialen: Rogers RO4350B (εr=3,48), Isola I-Tera MT40 (εr=3,45) en andere materialen met laag verlies zijn ideale keuzes.

- Beperkingen van traditioneel FR4: Grote diëlektrische constante schommelingen (4,2-4,7) en hoge verlies tangens (0,02) maken het ongeschikt voor toepassingen boven 10 GHz.

- Koperfolie selectie: Low-profile koperfolie (LP folie) vermindert de oppervlakteruwheid met 30% in vergelijking met standaard folie, waardoor de hoogfrequente verliezen aanzienlijk afnemen.

Expert Tip: Overweeg voor millimetergolffrequenties (24 GHz en hoger) materialen met ultralaag verlies zoals Rogers RT/duroid 5880 (εr=2,2).

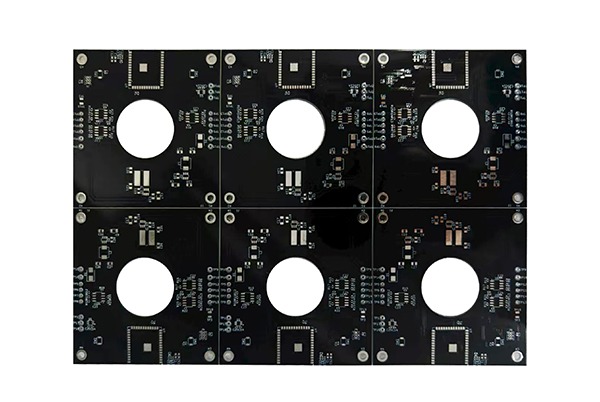

2.Gelamineerd ontwerp

Een uitstekend stapelontwerp moet rekening houden met:

- Symmetrische structuur: Voorkomt kromtrekken van de printplaat, zoals een “signaal-aarde-signaal” symmetrische opstelling.

- Dikte tussenlaag: Typische aanbevolen waarden:

- Opbouwlaag single-ended 50Ω:Diëlektrische dikte van 5-6mil (spoorbreedte 8-10mil).

- Binnenlaag single-ended 50Ω:Diëlektrische dikte van 4-5mil (spoorbreedte 5-7mil).

- Referentievlakken: Zorg ervoor dat signaallagen grenzen aan volledige aardvlakken, zodat splitsingen worden vermeden.

Casestudent ~4,3-4,8)Een 6-laags bord geoptimaliseerd voor stack-up verbeterde signaalintegriteit met 40%:

Laag1:Signaal (microstrip)

Laag2: Massief massavlak

Laag3: Signaal (striplijn)

Laag4: Signaal (striplijn)

Laag5: Massieve massaplaat

Laag6: Signaal (microstrip) Raadpleeg een professioneel PCB-ontwerpEen wetenschappelijk laagstapelontwerp garandeert de betrouwbaarheid van PCB's.

3.Ontwerp van bedrading

Impedantieformule (microstripbenadering):

Z₀ ≈ (87/√(εr+1,41)) × ln(5,98h/(0,8w+t))

Waar:

- Z₀: Karakteristieke impedantie (Ω)

- εr:Relatieve diëlektrische constante

- h:Diëlektrische dikte (mil)

- w:Spoorbreedte (mil)

- t:Koperdikte (mil)

Praktische tips:

- Gebruik Polar Si9000 of Altium impedantiecalculators voor nauwkeurige berekeningen.

- Volg de “3W-regel” voor differentiële paren: Afstand ≥ 3× spoorbreedte.

- Kritieke signaallengten binnen ±5mil tolerantie.

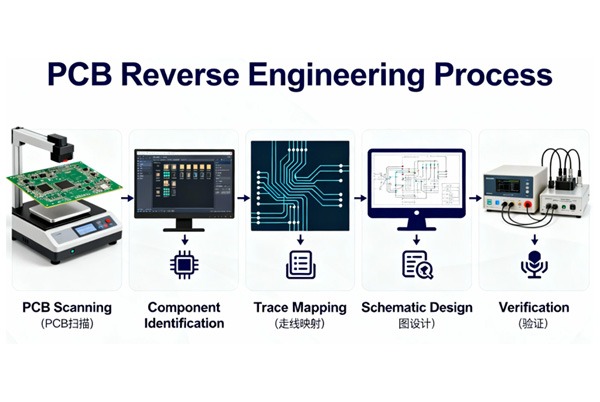

4.Productieproces

Wanneer je samenwerkt met PCB-fabrikantenbevestigen:

- Impedantietolerantie: Gewoonlijk ±10%, ±7% voor hoogwaardige toepassingen.

- Afgewerkte koperdikte: 1oz koper ≈ 1,4mil (35μm) werkelijke dikte.

- Diëlektrische Diktevariatie: Gewoonlijk binnen ±10%.

- Afwerking oppervlakENIG is beter dan HASL voor hoogfrequente toepassingen.

Veelvoorkomende problemen met impedantieregeling & oplossingen

Vraagstuk 1: via-geïnduceerde impedantiediscontinuïteit

Oplossingen:

- Gebruik terugboren om overtollige via stubs te verwijderen.

- Voeg aardingsvias toe in de buurt van kritieke signaalvias (afstand <150mil).

- Gebruik microvia's (<6mil) om parasitaire effecten te verminderen.

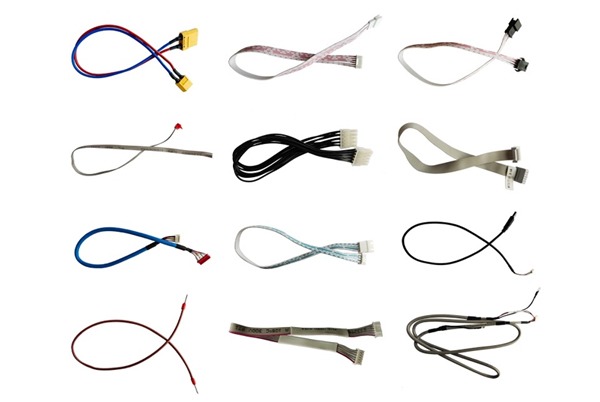

Probleem 2: Impedantie van de overgangszone van de connector komt niet overeen

Oplossingen:

- Ontwerp taps toelopende sporen voor soepele impedantieovergangen.

- Gebruik coplanaire golfgeleiderstructuren om de aardingscontinuïteit te verbeteren.

- Selecteer impedantie-afgestemde connectoren (bijvoorbeeld Samtec SEARAY-serie).

Probleem 3: Randstraling veroorzaakt impedantiefluctuatie

Oplossingen:

- Pas de “20H regel” toe: Power plane inzet door 20× diëlektrische dikte.

- Voeg ground via arrays toe langs de randen (afstand <λ/10).

- Elektromagnetische bandkloof (EBG) structuren toepassen om randstraling te onderdrukken.

Casestudie: 10Gbps SerDes kanaalimpedantieoptimalisatie

Uitdaging: Een PCB van een bedrijfsswitch vertoonde intermitterende gegevensfouten.

Analyse:

- TDR-tests onthulden een impedantievariatie van 15%.

- Oorzaak: Onvoldoende massavia's rond differentiële paren.

- Oppervlaktesporen hielden geen rekening met soldeermasker-effecten.

Oplossing:

- Verhoogde grond via dichtheid (één per 200 miljoen).

- Aangepaste spoorbreedte voor soldeermaskercompensatie (5mil→4,8mil).

- Overgeschakeld op soldeermasker met laag Dk-gehalte (εr=3,0).

Resultaat: Impedantie variatie gereduceerd tot <5%, bit error rate verbeterd met 100×!

Professioneel ontwerp voor impedantieregeling advies om uw elektronische ontwerp te beschermen.

Opkomende technologieën

- Materialen met ultralaag verliesbijv. Panasonic MEGTRON6 (Df=0,002).

- Hybride diëlektrische technologie: Combineren van materialen met verschillende Dk-waarden voor gelokaliseerde impedantieoptimalisatie.

- 3D-geprinte printplaten: Gegradueerde impedantiestructuren mogelijk maken.

- AI-ondersteund ontwerpOptimalisatie van impedantienetwerken automatiseren.

Checklist voor ingenieurs

Verifieer voordat u PCB's laat maken:

Bevestigde materiaalspecificaties en procesmogelijkheden met de fabrikant.

Impedantiesimulatie uitgevoerd voor kritieke netten.

Voldoet aan de vereisten voor het afstemmen van de lengte van het differentiële paar.

Geoptimaliseerd via structuren.

Ontworpen testcoupons.

Gedocumenteerde impedantiespecificaties.

Met de snelle ontwikkeling van 5G-, AI- en IoT-technologieën zal de vraag naar high-speed signaalintegriteit alleen maar toenemen. Door de kerntechnologie van PCB impedantieregeling te beheersen, kunt u uitblinken in het ontwerpen van high-speed PCB's en de stabiliteit en betrouwbaarheid van uw producten garanderen.

Verwante berichten