Yleiset ongelmat PCB:n luotettavuuden parantamisessa

Sisällysluettelo

Kuinka laskea PCB-impedanssi?

Piirilevyimpedanssin laskeminen varmistaa signaalin eheyden erityisesti nopeiden ja RF-piirien osalta.

1. Määritä PCB Stackup & Geometria

- Kerrosten lukumäärä: Yksi-, kaksi- tai monikerroksinen.

- Jäljen leveys (W) ja paksuus (T): Kriittinen impedanssin hallinnan kannalta.

- Dielektrinen paksuus (H): Signaalikerroksen ja vertailutason (esim. maan) välinen etäisyys.

- Kuparin paino: Tyypillisesti 0,5 oz (17,5 µm) - 2 oz (70 µm).

2. Tunnista dielektrinen vakio (Dk tai εᵣ).

- FR-4: ~4.3-4.8 (vaihtelee taajuuden mukaan).

- Rogers RO4003C: ~3.38 (RF:n matalahäviö).

- Polyimidi: ~3.5 (joustavat PCB:t).

- Huomautus: Dk pienenee hieman korkeammilla taajuuksilla.

3. Valitse impedanssin laskentamenetelmä

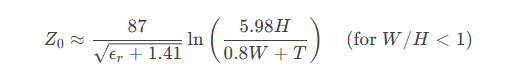

Mikroliuska (ulomman kerroksen jälki maatason päällä):

Nauhalinja (kahden maatason välinen sisäkerros):

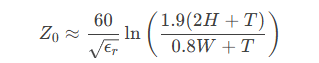

Differentiaalipari: Vaatii jälkien välisen etäisyyden (S).

4. Käytä impedanssilaskureita tai työkaluja

- Online-työkalut: Saturn PCB Toolkit, EEWeb Calculator.

- PCB-ohjelmisto: Altium Designer, KiCad tai Cadence sisältävät sisäänrakennetut impedanssilaskurit.

- EM-simulaattorit: Ansys HFSS, CST (edistyneille suunnitelmille).

5. Suunnittelun optimointi tulosten perusteella

- Säädä jäljen leveys (↑ leveys → ↓ impedanssi).

- Muokkaa dielektrinen paksuus (↑ H → ↑ impedanssi).

- Tweak jäljitysväli differentiaalisten parien osalta.

- Valitse materiaalit asianmukaisella Dk:lla (esim. Rogers RF:n osalta).

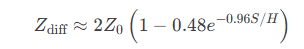

Esimerkkilaskelma (FR-4 mikroliuska)

Annettu:

- Jäljen leveys (W) = 0,2 mm.

- Dielektrinen paksuus (H) = 0,15 mm.

- Kuparin paksuus (T) = 0,035 mm.

- εᵣ = 4,5 %.

Mikroliuska kaavan avulla:

Vastaa RF-signaalien vakioimpedanssia 50Ω.

Miten signaalin eheys otetaan huomioon PCB-suunnittelu?

1. Asettelun suunnittelu

Piirilevyn ulkoasun suunnittelussa on tärkeää ottaa huomioon signaalijohtojen, virtajohtojen ja maajohtojen asettelu ja välttää signaalijohtojen, virtajohtojen ja maajohtojen risteämisen aiheuttamat häiriöt. Lisäksi on tärkeää minimoida signaalijohtojen pituus ristikkäisviestinnän ja viiveen vähentämiseksi.

2. Impedanssin sovitus

Kun suunnitellaan nopeita signaalijohtoja, impedanssin sovitus on suoritettava sen varmistamiseksi, että signaalijohtojen impedanssi vastaa signaalilähteen ja kuorman impedanssia, jolloin vältetään signaalin heijastuminen ja ristikkäishäirintä.

3. Signaalilinjan reititys

Piirilevysuunnittelussa signaalijohtojen reititys vaikuttaa myös signaalin eheyteen, ja sen on noudatettava tiettyjä sääntöjä. Esimerkiksi differentiaalisten signaalijohtojen on säilytettävä tietty välimatka ja ne on reititettävä rinnakkain, kun taas yksipuoliset signaalijohdot on reititettävä yhdensuuntaisesti maajohtojen kanssa, ja signaalijohtojen mutkat on minimoitava.

4. Virta ja maadoitus

Piirilevysuunnittelussa virran ja maadoituksen suunnittelu vaikuttaa myös signaalin eheyteen. Olisi käytettävä vakaata virtaa ja maadoitusta, ja virran ja maadoituksen resistanssi ja induktanssi olisi minimoitava mahdollisimman paljon.

5. Simuloinnin todentaminen

Kun piirilevysuunnittelu on valmis, simuloinnin todentaminen on tarpeen sen varmistamiseksi, että signaalin eheys täyttää vaatimukset. Simuloinnin avulla voidaan havaita signaaliviiveen, heijastuksen ja ristikkäisviestinnän kaltaiset ongelmat ja optimoida piirilevysuunnittelu.

Miten sähkömagneettinen yhteensopivuus (EMC) otetaan huomioon PCB-suunnittelussa?

1. PCB-asettelu EMC:tä varten

- Minimoi rinnakkainen reititys: Vältä pitkiä rinnakkaisia juoksuja signaalin ja teho-/maajohtimien välillä ristikkäisäänen ja sähkömagneettisen kytkennän vähentämiseksi.

- Kriittisten signaalien eristäminen: Erottele nopeat (esim. kellot, RF) ja herkät analogiset signaalit meluisista piireistä (esim. kytkentävirtalähteet).

- Kerroksen pinoamisstrategia:

- Käytä signaalikerrosten vieressä olevia kiinteitä maatasoja suojauksen aikaansaamiseksi.

- Reititä suurnopeussignaalit sisäkerroksissa maatasojen välissä eristämistä varten.

2. Maadoitustekniikat

- Matalaimpedanssiset maatasot: Käytä katkeamattomia maatasoja maasilmukoiden minimoimiseksi ja säteilypäästöjen vähentämiseksi.

- Jaa maa-alueet huolellisesti: Erottele analogiset/digitaaliset maadoitukset toisistaan vain tarvittaessa yhdellä liitäntäpisteellä (esim. ferriittihelmellä tai 0Ω-vastuksella).

- Via Stitching: Aseta useita maadoitusläpivientejä korkeataajuisten jälkien tai levyn reunojen ympärille onteloresonanssien vaimentamiseksi.

3. Suodatus ja tukahduttaminen

- Ferriittihelmet: Lisää virta/IO-linjoihin korkeataajuisten häiriöiden estämiseksi.

- Kytkentäkondensaattorit: Sijoita IC:n virtanastojen läheisyyteen (esim. 0,1μF + 1μF) suodattamaan korkeiden ja keskitaajuuksien kohinaa.

- Common-Mode-kuristimet: Käytä differentiaalipareissa (esim. USB, Ethernet) yhteismuotoisen säteilyn vaimentamiseksi.

4. Suojaus ja rajapintojen suunnittelu

- Kaapelin suojaus: Käytä suojattuja liittimiä (esim. USB, HDMI), jotka on maadoitettu 360° alustaan.

- Levytason suojaus: Lisää metallipurkkeja tai johtavia pinnoitteita herkkien RF-piirien päälle.

- Reunan suojaus: Reititä herkät jäljet pois hallituksen reunoilta; käytä suojapolkuja tai maadoitettua kuparivalua niiden ympärillä.

5. Simulointi ja testaus

- Pre-Layout-analyysi: Käytä ANSYS HFSS:n tai CST:n kaltaisia työkaluja säteilyn hotspottien mallintamiseen.

- Post-Layout-tarkastus:

- Suorita lähikenttäskannauksia päästölähteiden tunnistamiseksi.

- Suorita vaatimustenmukaisuustestaukset (esim. FCC, CE) säteily- ja johdettujen päästöjen osalta.

- Suunnittelun iterointi: Optimoi testitulosten perusteella (esim. lisäämällä terminointivastuksia tai säätämällä jälkien väliä).

Esimerkkikorjaukset:

- 100 MHz:n kello säteilee liikaa: Lisää sarjakiinnitysvastuksia tai reititä maatasojen väliin.

- Kytkentävirtalähteen melu: Toteuta π-suodattimet (LC) tuloon/lähtöön.

Integroimalla nämä käytännöt piirilevyt voivat täyttää EMC-standardit (esim. IEC 61000) ja samalla minimoida kalliit uudelleensuunnittelut. Prototyypit ja testit aina varhaisessa vaiheessa!

Kuinka ottaa huomioon Power Integrity (PI) PCB-suunnittelussa?

1. Tehon jäljityksen asettelu

- Lyhyet ja leveät jäljet: Minimoi vastus (R) ja loisinduktanssi (L) jännitehäviön ja kohinan vähentämiseksi.

- Vältä rinnakkaista reititystä signaalijäljitelmillä: Estä tehokohinan kytkeytyminen herkkiin signaaleihin (esim. kellot, analogiset piirit).

- Kerrosstrategia:

- Monikerroksisissa levyissä on varattava kokonaisia kerroksia virta- ja maatasoille.

- Kriittisillä virtakiskoilla (esim. suorittimen ydinjännite) olisi oltava omat virtatasot.

2. Tehon suodatus

- Kytkentäkondensaattorit:

- Irtoelektrolyyttikondensaattorit (10-100μF) virransyötöissä jännitteen vakauttamiseksi.

- Pienet keraamiset kondensaattorit (0,1μF) IC:n nastojen läheisyydessä korkeataajuisen kohinan suodattamiseksi.

- LC-suodattimet:

- Lisää π-suodattimia (kondensaattori + induktori) melulle herkille moduuleille (esim. PLL:t).

3. Virta ja maadoitus

- Matalaimpedanssiset paluureitit:

- Käytä kiinteitä maatasoja; vältä impedanssikatkoksia aiheuttavia jakoja.

- Useita läpivientejä teho- ja maatasojen yhdistämiseksi (vähentää läpivienti-induktanssia).

- Tähti maadoitus:

- Erilliset suuritehoiset ja herkät piirit, joissa on yhden pisteen maadoitus.

4. Simulointi ja validointi

- PDN (Power Delivery Network) -analyysi:

- Kohdeimpedanssi: ( Z_{\text{target}} = \frac{\Delta V}{\Delta I} ).

- Työkalut: ANSYS SIwave, Cadence Sigrity.

- Rippeli- ja melutestaus:

- Tarkista tehokohinan tasot oskilloskoopeilla tai simuloinneilla.

Kuinka sisällyttää testattavuuden suunnittelu (DFT) PCB-suunnitteluun?

1. Testipisteet ja liitännät

- Kriittisten signaalien testauspisteet:

- Tarjoa läpivientiä tai tyynyjä (halkaisija ≥1mm, väli ≥2,54mm), jotta koettimelle pääsee käsiksi.

- Merkitse testipisteet (esim. TP1, TP2).

- Standardiliitännät:

- Sijoita JTAG-, UART- tai SWD-liitännät lähelle levyn reunoja.

2. Levyn merkintä (silkkipaino)

- Komponenttien merkinnät:

- Merkitse viitenumerot (esim. R1, C2), napaisuus (+/-) ja nasta 1.

- Käytä korkeakontrastista silkkipainatusta (valkoinen/musta).

- Toiminnalliset alueet:

- Hahmottele alueet (esim. "Power Section"), jotta ne on helppo tunnistaa.

3. Ohjelmoitavat testitekniikat

- Boundary Scan (JTAG):

- IEEE 1149.1 -yhteensopivat IC:t (esim. FPGA:t, MCU:t) mahdollistavat liitäntätestauksen.

- Automatisoidut testauslaitteet (ATE):

- Testauslaitteen liitäntöjen varaaminen (esim. pogo tappityynyt).

4. Simulointi ja validointi

- DFT-sääntöjen tarkastukset:

- Varmistetaan testipisteiden kattavuus (esim. >90% käytettävissä olevia verkkoja).

- Vikatila-analyysi:

- Validoi testipiirit SPICE-simulaatioiden avulla.

Keskeiset suunnitteluperiaatteet Vertailu

| Virran eheys (PI) | Testattavuuden suunnittelu (DFT) |

|---|---|

| Matalaimpedanssinen tehonjakelu | Fyysisen testipisteen saavutettavuus |

| Kytkentäkondensaattorin optimointi | JTAG/rajapyyhkäisyn tuki |

| Minimoi teho-signaalikytkentä | Selkeä komponenttien/liitäntöjen merkintä |

| PDN-simulointi ja ripple-analyysi | ATE-yhteensopiva rakenne |

Esimerkkejä:

- PI-optimointi: DDR4-muistien tehotasot, joissa on useita 0805 0,1μF -korkkeja (tavoiteimpedanssi ≤0,1Ω).

- DFT-toteutus: Teollisuuden ohjaustaulu, jossa on 20 testipistettä automatisoitua lentävän koettimen testausta varten.

Suunnittelijat voivat parantaa virransyöttösuorituskykyä, testien tehokkuutta ja tuotannon luotettavuutta käsittelemällä PI:tä ja DFT:tä järjestelmällisesti.

Aiheeseen liittyvät viestit