Nykyaikaisessa elektroniikkateollisuudessa piirilevykokoonpanojen (PCBA) laatu määrittää suoraan lopputuotteen suorituskyvyn ja luotettavuuden. Tieto- ja viestintätekniikan (TVT) testilaitteet, kriittisenä toteuttamisvälineenä Piirin sisäinen testaus (ICT) eivät ole pelkkiä automatisoituja tarkastustyökaluja, vaan keskeisiä teknologisia laitteita, jotka mahdollistavat erittäin tarkan ja tehokkaan kokoonpanon tarkastuksen. Ne varmistavat järjestelmällisesti komponenttien oikean sijoittelun, napaisuuden, eheyden ja juotosliitoksen laadun tarkan sähköisen testauksen avulla, mikä mahdollistaa vikojen ennaltaehkäisyn ja laadunvalvonnan massavalmistuksessa.

TOPFAST, ammattimainen PCB-valmistaja, tarjoaa perusteellisen analyysin ICT-testilaitteiden toimintaperiaatteista, teknisistä eduista ja täytäntöönpanostrategioista. Tämä resurssi tarjoaa sekä syvyyttä että käytännön arvoa elektroniikan valmistusinsinööreille, laadunvalvonta-asiantuntijoille ja tuotantopäälliköille.

Sisällysluettelo

ICT-testiottelut: Määritelmä, rakenne ja tekninen merkitys

1.1 Mikä on ICT-testilaite?

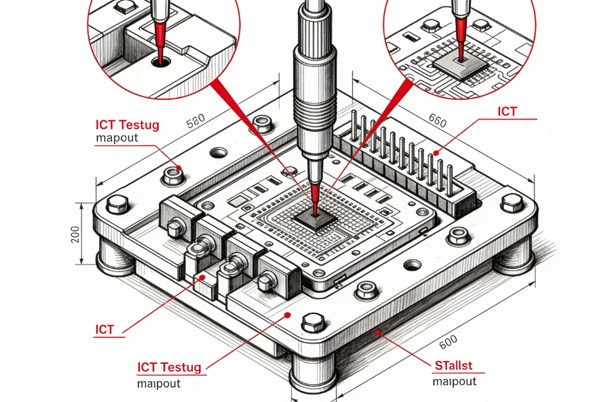

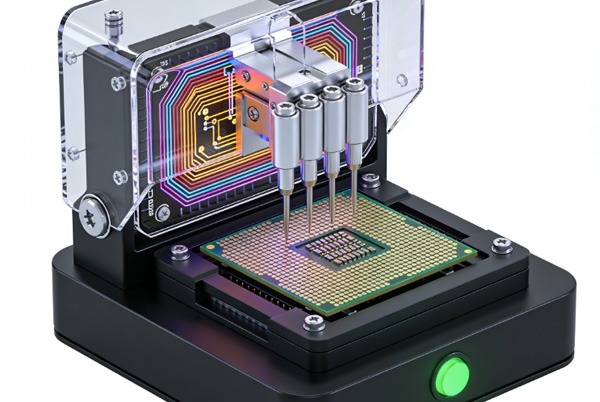

ICT-testilaite, jota kutsutaan usein "kynsien kiinnityslaitteeksi", on erittäin tarkka mekatroninen liitäntälaite, jota käytetään varmistamaan piirilevyn fyysinen kiinnitys ja sähköinen liitäntä automaattiseen testauslaitteistoon (ATE) testauksen aikana. Sen ydinrakenteeseen kuuluvat:

- Spring Probe Array: Räätälöity asettelu, joka perustuu piirilevyn esiasetettuihin testipisteisiin ja mahdollistaa monipisteisen synkronisen kontaktin.

- Kiinnikkeen pohjalevy ja kohdistusmekanismi: Varmistaa piirilevyn ja antureiden tarkan kohdistuksen.

- Toimintajärjestelmä: Esimerkiksi pneumaattiset, tyhjiö- tai mekaaniset lukitusmekanismit, jotka takaavat luotettavan puristusvoiman.

1.2 Tekninen merkitys: Varhainen vikojen havaitseminen ja taloudelliset vaikutukset

Tieto- ja viestintätekniikan testauksen ydinarvo on sen varhaisvaiheen vikojen havaitsemiskyky. Tutkimusten mukaan ICT-testaus välittömästi SMT-kokoonpanon jälkeen voi tunnistaa jopa 98% valmistusvirheitä, mikä vähentää myöhemmän vaiheen jälkityökustannuksia 30-50%. Korkean luotettavuuden aloilla, kuten autoelektroniikassa, lääkinnällisissä laitteissa ja ilmailu- ja avaruusalalla, tieto- ja viestintätekniikka on olennainen osa "virheetöntä" valmistusstrategiaa.

Toimialan näkemys: Kun piirilevyjen kokoonpanotiheys kasvaa ja komponentit pienenevät (esim. 01005-paketit), manuaalisella visuaalisella tarkastuksella ja AOI:lla on rajoituksia sähköisen suorituskyvyn todentamisessa. ICT tarjoaa suoran sähköisen signaalin mittauksen avulla korvaamatonta todentamissyvyyttä.

Miten ICT-testauksella saavutetaan neljä keskeistä todentamistoimintoa?

2.1 Komponentin oikean sijoittelun tarkistaminen

ICT määrittää, onko komponentti oikeassa paikassa ja spesifikaatioiden sisällä, mittaamalla sen sähköiset parametrit (vastus, kapasitanssi, induktanssi jne.). Esim:

- Vastuksen todentaminen: Testausjärjestelmä kytkee tunnetun virran komponentin yli, mittaa jännitehäviön ja laskee todellisen resistanssin.

- Kapasitanssin todentaminen: Mittaa kapasitiivisen impedanssin ominaisuutta vaihtosignaalilla.

Kun mittaukset jäävät esiasetettujen toleranssialueiden ulkopuolelle, järjestelmä merkitsee automaattisesti "virheellisen sijoittelun" tai "parametrien ajautumisen", mikä on erityisen hyödyllistä tunnistettaessa syöttövirheiden aiheuttamia erän väärän sijoittelun ongelmia.

2.2 Napaisuuden tarkistus: Avain virheettömyyteen

Napaisuudelle herkkien komponenttien (kuten diodien, elektrolyyttikondensaattoreiden ja integroitujen piirien) väärä suuntaus voi aiheuttaa piirin oikosulkuja, komponenttivaurioita tai jopa tulipalon vaaran. ICT suorittaa suuntaussähkötestauksen harkinnanvaraisesti:

- Dioditesti: Tarkistetaan eteenpäin suuntautuva jännitehäviö (~0,6-0,7 V) eteenpäin suuntautuvassa biasissa ja korkea impedanssi taaksepäin suuntautuvassa biasissa.

- Polarisoidun kondensaattorin testi: Arvioi asennussuunnan yhdistämällä kapasitanssimittauksen ja vuotovirran havaitsemisen.

2.3 Puuttuvan komponentin havaitseminen: Jatkuvuustestaus ja rinnakkaiset havaitsemistekniikat

ICT käyttää avoimen/lyhyen testejä komponenttien läsnäolon nopeaan määrittämiseen. Passiivisten komponenttien puuttuvat osat havaitaan mittaamalla solmujen välinen epätavallisen korkea impedanssi (avoin). Alueilla, joilla on useita komponentteja, kuten integroidut piirit, Boundary Scan tekniikka mahdollistaa laajamittaisen rinnakkaisen tunnistuksen, mikä parantaa merkittävästi testien tehokkuutta.

2.4 Juotosliitosten laadun arviointi: Sähköisestä liitettävyydestä luotettavuuden ennustamiseen.

Juotosliitoksen viat (kylmät juotosliitokset, riittämätön juote, silloitus jne.) ovat merkittävä syy ajoittaisiin vikoihin. ICT arvioi juotosliitosten sähköisen jatkuvuuden matalaresistanssimittauksella (usein käyttäen 4-johtimista Kelvinin ilmaisumenetelmää):

- Hyvä juotosliitos: Vastus on tyypillisesti alle 0,1Ω.

- Epäilyttävä juotosliitos: Resistanssi välillä 0,1-1Ω, mikä saattaa viitata mikrohalkeamiin tai riittämättömään juotokseen.

- Viallinen juotosliitos: Liian suuri vastus tai täysin avoin virtapiiri.

On tärkeää huomata, että vaikka ICT tunnistaa tehokkaasti sähköisten liitosten viat, sillä ei voida arvioida juotosliitosten mekaanista lujuutta tai visuaalisia vikoja. Siksi se yhdistetään usein Automaattinen optinen tarkastus (AOI) or Automaattinen röntgentarkastus (AXI) täydentävän testausstrategian muodostamiseksi.

ICT-testauslaitteiden tyypit ja valintaopas

| Valaisimen tyyppi | Sovellettavat skenaariot | Edut | Rajoitukset |

|---|---|---|---|

| Tyhjiö kiinnike | Suuritiheyksiset PCB:t, massatuotanto | Korkea kohdistustarkkuus, erinomainen testin johdonmukaisuus | Korkeat aloituskustannukset, vaatii tyhjiöjärjestelmän huoltoa |

| Pneumaattinen kiinnike | Keskisuuri tai suuri määrä, nopeat testisyklit | Vakaa kiinnitys, nopea toimintanopeus | Vaatii ilmansyötön, voi olla meluisa. |

| Manuaalinen kiinnike | Prototyyppien verifiointi, pieni volyymi, T&K-vianmääritys | Alhaiset kustannukset, suuri joustavuus | Alhainen testin tehokkuus, operaattorista riippuvainen |

| Custom Bed-of-Nails kiinnike | Monimutkaiset piirilevyt, korkean nastamäärän laitteet | Korkea testien kattavuus, korkea skaalautuvuus | Pitkä suunnittelun läpimenoaika, korkeat räätälöintikustannukset |

Valintasuositukset:

- Massatuotannossa, kuten autoelektroniikassa, on tyhjiökiinnike, jossa on erittäin tiheät anturit suositellaan testin vakauden varmistamiseksi.

- Monenlaisten, pienen volyymin teollisten ohjaustaulujen osalta on käytettävä modulaarinen pneumaattinen kiinnitin voi tasapainottaa investointeja ja joustavuutta.

Parhaat käytännöt tieto- ja viestintätekniikan testauksen toteuttamiseen ja testattavuuden suunnitteluun (Design for Testability, DFT).

4.1 Testattavuuden suunnittelun (DFT) periaatteet

- Tarjoa testipisteet: Suunnittele testialustat, joiden halkaisija on ≥0,9 mm, kaikkiin kriittisiin verkon solmukohtiin.

- Vältä esteitä: Säilytä 5 mm:n etäisyys testipisteiden ympärillä korkeista komponenteista.

- Eristä virta ja maadoitus: Mahdollistaa eristetyn tehoverkon testauksen testinastojen avulla vianeristystarkkuuden parantamiseksi.

- Sisällytä Boundary Scan: Integroidaan JTAG-liitännät monimutkaisia integroituja piirilevyjä varten (esim. FPGA:t, prosessorit), jotta voidaan parantaa hallittavuutta ja tarkkailtavuutta.

Prosessien integrointi ja tietojen analysointi

- Testausohjelman luominen: Luo testivektorit automaattisesti CAD-tiedoista ohjelmointiajan lyhentämiseksi.

- Tietojen jäljitettävyys: Yhdistä ICT-testien tulokset tuotantoeriin ja komponenttieriin laadun jäljitettävyyden varmistamiseksi.

- Trendianalyysi: Käytä tilastollista prosessinohjausta (SPC) prosessin poikkeamien tunnistamiseen (esim. juotospastan tulostusongelmat, reflow-profiilin poikkeamat).

Tekniset haasteet ja tuleva kehitys

5.1 Nykyiset haasteet

- Miniatyrisointirajat: Fyysisen anturikontaktin vaikeutuminen lisääntyy, kun pakkauskoko pienenee alle 0201:n.

- Korkean taajuuden testauksen rajoitukset: RF-piirien (>1 GHz) sähköinen testaus edellyttää erikoistuneita impedanssin sovitussuunnitelmia.

- Joustavan levyn testaus: Joustavien painettujen piirien (Flexible Printed Circuits, FPC) kohdistus- ja kosketusvakautta koskevat korkeammat vaatimukset.

5.2 Teknologiset suuntaukset

- Kosketuksettomat testaustekniikat: Flying Probe -testauksen ja tieto- ja viestintätekniikan yhdistäminen, jotta voidaan mukautua korkean sekoituksen tuotantoon.

- Älykkäät valaisimet: Antureiden integrointi anturin paineen ja kosketusvastuksen reaaliaikaiseen seurantaan, mikä mahdollistaa ennakoivan huollon.

- Data-fuusion testaus: Tekoälyn käyttö ICT-tietojen yhdistämiseen AOI-, AXI- ja toiminnallisten testitulosten kanssa kattavan laatuprofiilin luomiseksi.

Päätelmä

Tieto- ja viestintätekniikan testauslaitteet eivät ole pelkkiä tarkastustyökaluja, vaan ne ovat suunnittelun, valmistuksen ja laadunhallinnan kattavan järjestelmäteknisen lähestymistavan kantajia. Tarkan sähköisen todentamisen avulla ne varmistavat, että sijoitusvirheitä, käänteisiä napaisuuksia ja juotosvirheitä ei esiinny, ja parantavat näin olennaisesti PCBA:n luotettavuutta. Älykkäiden tehtaiden ja teollisuus 4.0:n kehittyessä tieto- ja viestintätekniikka integroituu syvällisesti IoT:hen ja big data -analytiikkaan, ja se kehittyy "vikojen havaitsemisesta" kohti "prosessin optimointia ja ennustamista".

Valmistuksen huippuosaamista tavoitteleville yrityksille investoiminen kehittyneisiin tieto- ja viestintätekniikan testausratkaisuihin ei ole vain laadunvarmistustoimenpide vaan myös keskeinen strategia markkinoiden kilpailukyvyn parantamiseksi ja elinkaaren kokonaiskustannusten alentamiseksi.

Tieto- ja viestintätekniikan testauslaitteiden haasteet ja vastatoimet

Ydinkonflikti: Korkea alkuinvestointi verrattuna pitkän aikavälin tuottoihin.

Ratkaisu: Suorita Kokonaiskustannusten analyysi (TCO), määrällisesti arvioiden myöhäisvaiheen jälkityön, romun ja mainehaittojen välttämiskustannukset, jotka aiheutuvat virheiden varhaisesta havaitsemisesta. Aloita pilottikokeilu pienellä erällä kriittisiä tuotteita, jotta voit osoittaa ROI:n tietojen avulla.

A: Ydinkonflikti: Suuritiheyksiset, miniatyrisoidut piirilevymallit ilman fyysistä anturikontaktia.

Ratkaisu: IntegrateessSuunnitteluohjeet: Testattavuuden suunnittelu (DFT) piirilevyn asetteluvaiheen alkuvaiheessa, jolloin testipisteiden sijoittelu on pakollista. Hyödynnä mikro-anturit, Boundary Scan (JTAG), - mikro-anturit, Boundary Scan (JTAG), tai täydentää Lentävän koettimen testaus.

A: Ydinkonflikti: Monimutkainen, aikaa vievä ohjelmointi verrattuna tarpeeseen mukautua nopeasti suunnittelun muutoksiin.

Ratkaisu: Hyödynnä ohjelmistoja Automaattisesti luodaan testata ohjelmakehyksiä suunnittelutiedostoista, luoda kirjasto vakiokomponenttitestejä varten ja toteuttaa tiukka ohjelmien versionhallinta.

A: Ydinkonflikti: Koettimet ovat kulutustavaroita, kun taas vakaita ja luotettavia testituloksia vaaditaan.

Ratkaisu: Toteuta Ennaltaehkäisevän huollon aikataulu: päivittäinen puhdistus, säännöllinen huolto, säännöllinen kalibrointi ja kriittisten varaosien varaston ylläpitäminen.

A: Ydinkonflikti: Tieto- ja viestintätekniikka on erinomainen sähkötestauksessa, mutta se ei pysty havaitsemaan toiminnallisia, visuaalisia ja piilossa olevia vikoja.

Ratkaisu: Rakenna Yhdistelmätestausstrategia, tieto- ja viestintätekniikan integrointi SPI, AOI, AXI ja FCT muodostavat toisiaan täydentävän "testipyramidin" kattavan kattavuuden varmistamiseksi.