Almindelige problemer med at forbedre PCB-pålidelighed

Indholdsfortegnelse

Hvordan beregner man PCB-impedans?

Beregning af PCB-impedans sikrer signalintegritet, især for højhastigheds- og RF-kredsløb.

1. Bestem PCB-stackup og -geometri

- Antal lag: Enkelt, dobbelt eller flere lag.

- Sporbredde (W) og tykkelse (T): Kritisk for impedansstyring.

- Dielektrisk tykkelse (H): Afstand mellem signallag og referenceplan (f.eks. jord).

- Vægt i kobber: Typisk 0,5 oz (17,5 µm) til 2 oz (70 µm).

2. Identificer dielektrisk konstant (Dk eller εᵣ)

- FR-4: ~4,3-4,8 (varierer med frekvensen).

- Rogers RO4003C: ~3,38 (lavt tab til RF).

- Polyimid: ~3,5 (fleksible printkort).

- Bemærk: Dk falder en smule ved højere frekvenser.

3. Vælg metode til impedansberegning

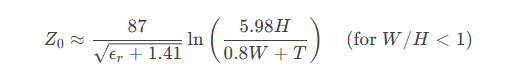

Microstrip (sporing af det ydre lag over jordplanet):

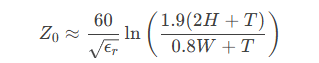

Stripline (indre lag mellem to jordplaner):

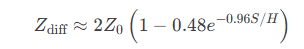

Differentielt par: Kræver afstand (S) mellem sporene.

4. Brug impedansberegnere eller -værktøjer

- Online-værktøjer: Saturn PCB Toolkit, EEWeb Calculator.

- PCB-software: Altium Designer, KiCad eller Cadence har indbyggede impedansberegnere.

- EM-simulatorer: Ansys HFSS, CST (til avancerede designs).

5. Optimer design baseret på resultater

- Juster Sporbredde (↑ bredde → ↓ impedans).

- Ændre dielektrisk tykkelse (↑ H → ↑ impedans).

- Tweak sporafstand for differentielle par.

- Vælg materialer med passende Dk (f.eks. Rogers for RF).

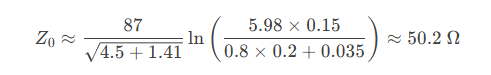

Eksempel på beregning (FR-4 mikrostrip)

Givet:

- Sporbredde (W) = 0,2 mm

- Dielektrisk tykkelse (H) = 0,15 mm

- Kobbertykkelse (T) = 0,035 mm

- εᵣ = 4,5

Ved hjælp af mikrostripformlen:

Matcher standard 50Ω-impedans for RF-signaler.

Hvordan man overvejer signalintegritet i PCB-design?

1. Design af layout

I PCB-layoutdesign er det vigtigt at overveje layoutet af signallinjer, strømledninger og jordledninger og at undgå interferens forårsaget af krydsning af signallinjer, strømledninger og jordledninger. Derudover er det vigtigt at minimere længden af signallinjer for at reducere krydstale og forsinkelse.

2. Impedanstilpasning

Når man designer højhastighedssignallinjer, skal der foretages impedanstilpasning for at sikre, at signallinjernes impedans svarer til signalkildens og belastningens impedans, så man undgår signalrefleksion og krydstale.

3. Signal linjeføring

I PCB-design påvirker routing af signallinjer også signalintegriteten og skal følge visse regler. For eksempel skal differentielle signallinjer holde en vis afstand og føres parallelt, mens single-ended signallinjer skal føres parallelt med jordlinjer, og signallinjebøjninger skal minimeres.

4. Strøm og jordforbindelse

I PCB-design påvirker designet af strøm og jordforbindelse også signalintegriteten. Der skal bruges stabil strøm og jordforbindelse, og modstanden og induktansen i strøm og jordforbindelse skal minimeres så meget som muligt.

5. Verifikation af simulering

Når PCB-designet er færdigt, er det nødvendigt med simuleringsverifikation for at sikre, at signalintegriteten opfylder kravene. Gennem simulering kan problemer som signalforsinkelse, refleksion og krydstale opdages, og PCB-designet kan optimeres.

Hvordan overvejer man elektromagnetisk kompatibilitet (EMC) i PCB-design?

1. PCB-layout til EMC

- Minimér parallel routing: Undgå lange parallelle forløb mellem signal- og strøm-/jordledninger for at reducere krydstale og elektromagnetisk kobling.

- Isolering af kritiske signaler: Adskil højhastighedssignaler (f.eks. ure, RF) og følsomme analoge signaler fra støjende kredsløb (f.eks. switching strømforsyninger).

- Strategi for lagopbygning:

- Brug solide jordplaner ved siden af signallagene for at give afskærmning.

- Før højhastighedssignaler på de indre lag mellem jordplanerne for at inddæmme dem.

2. Teknikker til jordforbindelse

- Jordplaner med lav impedans: Brug ubrudte jordplaner for at minimere jordsløjfer og reducere udstråling.

- Del jorden forsigtigt op: Adskil kun analog/digital jord, når det er nødvendigt, med et enkelt forbindelsespunkt (f.eks. ferritperle eller 0Ω-modstand).

- Via Stitching: Placer flere ground vias omkring højfrekvente spor eller kortkanter for at undertrykke hulrumsresonanser.

3. Filtrering og undertrykkelse

- Ferritperler: Tilføjes til strøm-/IO-linjer for at blokere højfrekvent støj.

- Afkoblingskondensatorer: Placer nær IC's strømstifter (f.eks. 0,1 μF + 1 μF) for at filtrere høj- og mellemfrekvent støj.

- Common-Mode-drossler: Bruges på differentielle par (f.eks. USB, Ethernet) til at undertrykke common-mode-stråling.

4. Afskærmning og grænsefladedesign

- Afskærmning af kabler: Brug afskærmede stik (f.eks. USB, HDMI) med 360° jordforbindelse til kabinettet.

- Afskærmning på tavleniveau: Tilføj metaldåser eller ledende belægninger over følsomme RF-kredsløb.

- Beskyttelse af kanter: Før følsomme spor væk fra kortets kanter; brug beskyttelsesspor eller jordet kobber omkring dem.

5. Simulering og afprøvning

- Analyse før layout: Brug værktøjer som ANSYS HFSS eller CST til at modellere strålingshotspots.

- Verifikation efter layout:

- Udfør nærfeltscanninger for at identificere emissionskilder.

- Udfør overensstemmelsestest (f.eks. FCC, CE) for udstrålede/ledte emissioner.

- Design-iteration: Optimer baseret på testresultater (f.eks. tilføjelse af afslutningsmodstande eller justering af sporafstand).

Eksempler på rettelser:

- Et ur på 100 MHz udstråler for meget: Tilføj serieafslutningsmodstande, eller led mellem stelplanerne.

- Støj fra switching-strømforsyningen: Implementer π-filtre (LC) ved input/output.

Ved at integrere disse fremgangsmåder kan printkort opfylde EMC-standarder (f.eks. IEC 61000) og samtidig minimere dyre redesigns. Lav altid prototyper og test tidligt!

Hvordan tager man højde for Power Integrity (PI) i PCB-design?

1. Power Trace-layout

- Korte og brede spor: Minimér modstand (R) og parasitisk induktans (L) for at reducere spændingsfald og støj.

- Undgå parallel routing med signalspor: Forhindrer, at strømstøj kobles ind i følsomme signaler (f.eks. ure, analoge kredsløb).

- Lag-strategi:

- I flerlagskort skal hele lag dedikeres til strøm- og jordplaner.

- Kritiske strømskinner (f.eks. CPU-kernespænding) bør have dedikerede strømplaner.

2. Filtrering af strøm

- Afkoblingskondensatorer:

- Elektrolytkondensatorer (10-100 μF) ved strømindgangene for at stabilisere spændingen.

- Små keramiske kondensatorer (0,1 μF) nær IC-stifter for at filtrere højfrekvent støj.

- LC-filtre:

- Tilføj π-filtre (kondensator + induktor) til støjfølsomme moduler (f.eks. PLL'er).

3. Strøm og jordforbindelse

- Returstier med lav impedans:

- Brug solide jordplaner; undgå splittelser, der forårsager impedansdiskontinuiteter.

- Flere vias til at forbinde strøm/jord-plan (reducerer via-induktans).

- Stjernejording:

- Adskil højeffekt- og følsomme kredsløb med enkeltpunktsjording.

4. Simulering og validering

- PDN-analyse (Power Delivery Network):

- Målets impedans: ( Z_{\text{target}} = \frac{\Delta V}{\Delta I} ).

- Værktøjer: ANSYS SIwave, Cadence Sigrity.

- Test af rystelser og støj:

- Verificer effektstøjniveauer med oscilloskoper eller simuleringer.

Hvordan inkorporerer man design for testbarhed (DFT) i PCB-design?

1. Testpunkter og grænseflader

- Testpunkter for kritiske signaler:

- Sørg for vias eller pads (diameter ≥1 mm, afstand ≥2,54 mm) for adgang til proben.

- Mærk testpunkterne (f.eks. TP1, TP2).

- Standard-grænseflader:

- Placer JTAG-, UART- eller SWD-grænseflader nær kortets kanter.

2. Mærkning af tavler (silketryk)

- Mærkning af komponenter:

- Mærk referencebetegnelser (f.eks. R1, C2), polaritet (+/-) og Pin 1.

- Brug silketryk med høj kontrast (hvid/sort).

- Funktionelle zoner:

- Skitsér områder (f.eks. "Power Section"), så de er nemme at identificere.

3. Programmerbare testteknikker

- Afgrænsningsscanning (JTAG):

- IEEE 1149.1-kompatible IC'er (f.eks. FPGA'er, MCU'er) muliggør test af sammenkoblinger.

- Automatiseret testudstyr (ATE):

- Reserver grænseflader til testarmaturer (f.eks. pogo-pads).

4. Simulering og validering

- Kontrol af DFT-regler:

- Sørg for testpunktsdækning (f.eks. >90% af tilgængelige net).

- Analyse af fejltilstand:

- Valider testkredsløb via SPICE-simuleringer.

Sammenligning af vigtige designprincipper

| Strømforsyningsintegritet (PI) | Design for testbarhed (DFT) |

|---|---|

| Strømfordeling med lav impedans | Fysisk tilgængelighed af testpunkter |

| Optimering af afkoblingskondensator | Understøttelse af JTAG/grænsescanning |

| Minimér koblingen mellem strøm og signal | Tydelig mærkning af komponenter/grænseflader |

| PDN-simulering og ripple-analyse | ATE-kompatibelt design |

Eksempler:

- PI-optimering: DDR4-hukommelsens strømforsyninger med flere 0805 0,1μF-kapsler (målimpedans ≤0,1Ω).

- DFT-implementering: Industrielt kontrolkort med 20 testpunkter til automatiseret test med flyvende probe.

Ved systematisk at arbejde med PI og DFT kan designere forbedre strømforsyningen, testeffektiviteten og produktionssikkerheden.

Relaterede indlæg