Veelvoorkomende problemen bij het verbeteren van PCB-betrouwbaarheid

Inhoudsopgave

Hoe PCB-impedantie berekenen?

Het berekenen van PCB-impedantie zorgt voor signaalintegriteit, vooral voor circuits met hoge snelheden en RF-circuits.

1. PCB-stapeling en -geometrie bepalen

- Aantal lagen: Enkel, dubbel of meerlagig.

- Spoorbreedte (W) en dikte (T): Kritisch voor impedantieregeling.

- Diëlektrische dikte (H): Afstand tussen de signaallaag en het referentievlak (bijv. aarde).

- Koper gewicht: Gewoonlijk 0,5 oz (17,5 µm) tot 2 oz (70 µm).

2. Diëlektrische constante (Dk of εᵣ) bepalen

- FR-4: ~4,3-4,8 (varieert met de frequentie).

- Rogers RO4003C: ~3,38 (met laag verlies voor RF).

- Polyimide: ~3,5 (flexibele printplaten).

- Noteant ~4,3-4,8): Dk neemt iets af bij hogere frequenties.

3. Impedantieberekeningsmethode kiezen

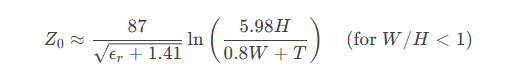

Microstrip (buitenste laag over massaplaat):

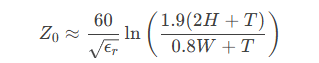

Striplijn (binnenste laag tussen twee grondvlakken):

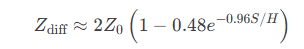

Differentieel paar: Vereist afstand (S) tussen de sporen.

4. Impedantieberekenaars of -hulpmiddelen gebruiken

- Online gereedschap: Saturn PCB Toolkit, EEWeb Calculator.

- PCB-software: Altium Designer, KiCad of Cadence hebben ingebouwde impedantieberekeningen.

- EM Simulatoren: Ansys HFSS, CST (voor geavanceerde ontwerpen).

5. Ontwerp optimaliseren op basis van resultaten

- Aanpassen spoorbreedte (↑ breedte → ↓ impedantie).

- Aanpassen diëlektrische dikte (↑ H → ↑ impedantie).

- Tweak Spoorafstand voor differentiële paren.

- Selecteer materialen met geschikte Dk (bijvoorbeeld Rogers voor RF).

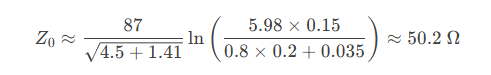

Voorbeeldberekening (FR-4 Microstrip)

Gegeven:

- Spoorbreedte (W) = 0,2 mm

- Diëlektrische dikte (H) = 0,15 mm

- Koperdikte (T) = 0,035 mm

- εᵣ = 4,5

Gebruik de microstripformule:

Komt overeen met de standaard 50Ω impedantie voor RF-signalen.

Hoe signaalintegriteit te overwegen in PCB-ontwerp?

1. Lay-outontwerp

Bij het PCB layout ontwerp is het belangrijk om rekening te houden met de layout van signaallijnen, voedingslijnen en aardlijnen en om interferentie te vermijden die veroorzaakt wordt door het kruisen van signaallijnen, voedingslijnen en aardlijnen. Daarnaast is het essentieel om de lengte van signaallijnen te minimaliseren om overspraak en vertraging te verminderen.

2. Impedantie-aanpassing

Bij het ontwerpen van hogesnelheidssignaalkabels moet impedantieaanpassing worden uitgevoerd om ervoor te zorgen dat de impedantie van de signaalkabels overeenkomt met de impedantie van de signaalbron en de belasting, waardoor signaalreflectie en overspraak worden vermeden.

3. Signaallijnroutering

Bij het PCB-ontwerp is de routing van signaallijnen ook van invloed op de signaalintegriteit en moet deze aan bepaalde regels voldoen. Differentiële signaallijnen moeten bijvoorbeeld een bepaalde afstand houden en parallel worden gerouteerd, terwijl single-ended signaallijnen parallel aan massalijnen moeten worden gerouteerd en bochten in signaallijnen tot een minimum moeten worden beperkt.

4. Voeding en aarding

Bij het PCB-ontwerp is het ontwerp van voeding en aarding ook van invloed op de signaalintegriteit. Er moet een stabiele voeding en aarding worden gebruikt en de weerstand en inductie van voeding en aarding moeten zoveel mogelijk worden geminimaliseerd.

5. Simulatieverificatie

Nadat het PCB-ontwerp is voltooid, is simulatieverificatie vereist om ervoor te zorgen dat de signaalintegriteit aan de vereisten voldoet. Door simulatie kunnen problemen zoals signaalvertraging, reflectie en overspraak worden opgespoord en kan het PCB-ontwerp worden geoptimaliseerd.

Hoe elektromagnetische compatibiliteit (EMC) overwegen bij het PCB-ontwerp?

1. PCB-indeling voor EMC

- Parallel routeren minimaliseren: Vermijd lange parallelle lijnen tussen signaal- en voedings-/massasporen om overspraak en elektromagnetische koppeling te beperken.

- Kritieke signaalisolatie: Scheid snelle (bijv. klokken, RF) en gevoelige analoge signalen van lawaaierige circuits (bijv. schakelende voedingen).

- Laagopbouwstrategie:

- Gebruik stevige aardvlakken naast de signaallagen om afscherming te bieden.

- Routeer hogesnelheidssignalen op binnenlagen tussen massaplaten voor insluiting.

2. Aardingstechnieken

- Aardingsplaten met lage impedantie: Gebruik ononderbroken aardvlakken om aardlussen te minimaliseren en uitgestraalde emissies te verminderen.

- Grond zorgvuldig verdelen: Scheid analoge/digitale aarding alleen als dat nodig is, met een enkel aansluitpunt (bijv. ferrietkraal of 0Ω weerstand).

- Via Stitching: Plaats meerdere aardingsvias rond hoogfrequente sporen of randen van de printplaat om holteresonanties te onderdrukken.

3. Filteren en onderdrukken

- Ferriet Kralen: Toevoegen aan voedings-/IO-lijnen om hoogfrequente ruis te blokkeren.

- Ontkoppelingscondensatoren: Plaats in de buurt van de voedingspinnen van het IC (bijv. 0,1μF + 1μF) om ruis van hoge en middenfrequenties te filteren.

- Gemeenschappelijke-mode smoorspoelen: Gebruik op differentiële paren (bijv. USB, Ethernet) om common-mode straling te onderdrukken.

4. Afscherming en interfaceontwerp

- Kabelafscherming: Gebruik afgeschermde connectoren (bijv. USB, HDMI) met 360° aarding naar het chassis.

- Afscherming op directieniveau: Plaats metalen blikken of geleidende coatings over gevoelige RF-circuits.

- Randbescherming: Leid gevoelige sporen weg van de randen van de printplaat; gebruik afschermsporen of geaard kopergiet eromheen.

5. Simulatie en testen

- Analyse vóór het ontwerp: Gebruik tools zoals ANSYS HFSS of CST om stralingshaarden te modelleren.

- Verificatie na layout:

- Nabij veld scans uitvoeren om emissiebronnen te identificeren.

- Conformiteitstests uitvoeren (bijv. FCC, CE) voor uitgestraalde/geleide emissies.

- Ontwerp Iteratie: Optimaliseren op basis van de testresultaten (bijvoorbeeld afsluitweerstanden toevoegen of de spoorafstand aanpassen).

Voorbeeldoplossingen:

- Een 100MHz klok straalt overmatig: Voeg seriële afsluitweerstanden toe of routeer tussen massaplaten.

- Ruis bij schakelende voeding: implementeer π-filters (LC) aan de ingang/uitgang.

Door deze praktijken te integreren, kunnen PCB's voldoen aan de EMC-normen (bijv. IEC 61000) en tegelijkertijd kostbare herontwerpen minimaliseren. Altijd vroeg prototypen en testen!

Hoe Power Integrity (PI) overwegen bij PCB-ontwerp?

1. Stroomspoorlay-out

- Korte en brede sporen: Minimaliseer weerstand (R) en parasitaire inductantie (L) om spanningsverlies en ruis te verminderen.

- Parallel routeren vermijden met signaalsporen: Voorkomen dat spanningsruis doorwerkt in gevoelige signalen (bijvoorbeeld klokken, analoge circuits).

- Laagstrategie:

- In meerlaagse borden moeten hele lagen worden gebruikt voor voedings- en aardingsvlakken.

- Kritische stroomrails (bijvoorbeeld CPU-kernspanning) moeten speciale stroomvlakken hebben.

2. Vermogen filteren

- Ontkoppelingscondensatoren:

- Bulk elektrolytische condensatoren (10-100μF) bij stroomingangen om de spanning te stabiliseren.

- Kleine keramische condensatoren (0,1μF) in de buurt van IC-pennen om hoogfrequente ruis te filteren.

- LC-filters:

- Voeg π-filters (condensator + inductor) toe voor ruisgevoelige modules (bijvoorbeeld PLL's).

3. Voeding en aarding

- Returnpaden met lage impedantie:

- Gebruik stevige aardvlakken; vermijd splitsingen die impedantiediscontinuïteiten veroorzaken.

- Meerdere vias om voedings-/ massavlakken te verbinden (vermindert via-inductantie).

- Ster-aarding:

- Scheid hoogvermogen- en gevoelige circuits, met enkelpolige aarding.

4. Simulatie en validatie

- PDN-analyse (Power Delivery Network):

- Doelimpedantie: ( Z_{doel}} = \frac{{Delta V}{{Delta I} ).

- Gereedschappen: ANSYS SIwave, Cadence Sigrity.

- Rimpeling en ruis testen:

- Controleer de ruisniveaus met oscilloscopen of simulaties.

Hoe Design for Testability (DFT) integreren in PCB-ontwerp?

1. Testpunten en interfaces

- Kritieke signaaltestpunten:

- Zorg voor vias of pads (diameter ≥1 mm, tussenruimte ≥2,54 mm) voor toegang tot de sonde.

- Label de testpunten (bijvoorbeeld TP1, TP2).

- Standaard interfaces:

- Plaats JTAG-, UART- of SWD-interfaces in de buurt van de randen van de printplaat.

2. Board-labeling (zeefdruk)

- Component Markeringen:

- Label referentieaanduidingen (bijv. R1, C2), polariteit (+/-) en pin 1.

- Gebruik contrastrijke zeefdruk (wit/zwart).

- Functionele zones:

- Omlijn gebieden (bijv. "Vermogenssectie") voor gemakkelijke identificatie.

3. Programmeerbare testtechnieken

- Grenswaarde scannen (JTAG):

- IEEE 1149.1-compatibele IC's (bijv. FPGA's, MCU's) maken interconnectietesten mogelijk.

- Geautomatiseerde testapparatuur (ATE):

- Reserveer interfaces voor testopstellingen (bijv. pogo pin pads).

4. Simulatie en validatie

- DFT Regelcontroles:

- Zorg voor testpuntdekking (bijv. >90% van toegankelijke netten).

- Foutmodusanalyse:

- Testcircuits valideren via SPICE-simulaties.

Belangrijkste ontwerpprincipes Vergelijking

| Integriteit van vermogen (PI) | Ontwerp voor testbaarheid (DFT) |

|---|---|

| Stroomverdeling met lage impedantie | Fysieke toegankelijkheid testpunt |

| Optimalisatie ontkoppelingscondensator | JTAG/grensverleggende scanondersteuning |

| Vermogen-signaalkoppeling minimaliseren | Duidelijke etikettering van onderdelen/interfaces |

| PDN-simulatie en rimpelanalyse | ATE-compatibel ontwerp |

Voorbeelden:

- PI optimalisatie: DDR4 geheugenvoedingsvlakken met meerdere 0805 0,1μF caps (doelimpedantie ≤0,1Ω).

- DFT-implementatie: Industriële besturingsprintplaat met 20 testpunten voor geautomatiseerde tests met vliegende sondes.

Door PI en DFT systematisch aan te pakken, kunnen ontwerpers de vermogensprestaties, testefficiëntie en productiebetrouwbaarheid verbeteren.

Verwante berichten