6-Lagen PCB Stacking Design und Herstellung

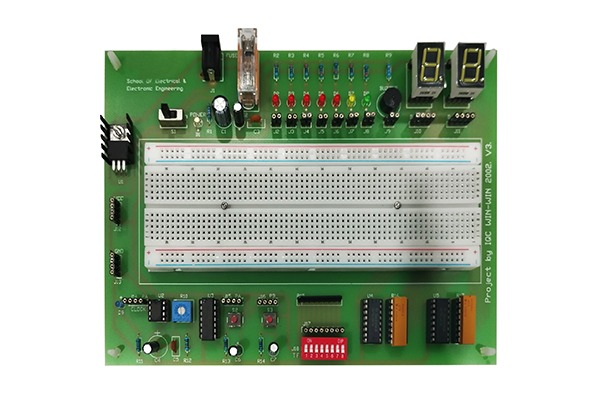

Elektronische Produkte entwickeln sich schnell weiter, und gedruckte Schaltplatten (PCBs) haben sich von einfachen ein- oder zweilagigen Strukturen zu komplexen mehrlagigen Leiterplatten mit sechs oder mehr Lagen entwickelt, um den wachsenden Anforderungen an die Bauteildichte und Hochgeschwindigkeitsverbindungen gerecht zu werden.

Sechslagige Leiterplatten bieten Ingenieuren eine größere Flexibilität beim Routing, verbesserte Möglichkeiten der Lagentrennung und optimierte Lösungen für die lagenübergreifende Schaltungsaufteilung. Eine gut durchdachte Konfiguration des sechslagigen Leiterplattenaufbaus, die Dickenberechnung, der Herstellungsprozess und die Signalintegrität sind entscheidende Schritte zur Verbesserung der Produktleistung und -zuverlässigkeit.

Inhaltsübersicht

6-Lagen-Leiterplattenstapel-Konfiguration

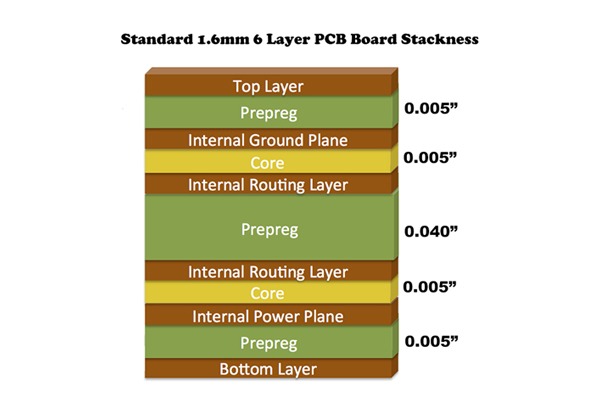

Die sechs leitenden Kupferschichten in einer Mehrlagen-Leiterplatte müssen in einer sorgfältig konzipierten Reihenfolge angeordnet und durch dielektrische Materialien getrennt werden. Ein vernünftiges Stapeldesign ist die Grundlage für die Gewährleistung der Signalintegrität, der Energieintegrität und der elektromagnetischen Verträglichkeit.

Standard-Layer-Reihenfolge und Funktionszuweisung

Angebot für PCB-Herstellung und -Bestückung anfordern

- Angebot für PCB-Herstellung und -Bestückung anfordern: Komponentenmontageschicht für Primärgeräte und partielles Routing

- Schicht 2: Bezugsebene (typischerweise Massefläche GND)

- Schicht 3: Innere Signalrouting-Schicht

- Schicht 4: Innere Signalführungsschicht oder Leistungsebene

- Schicht 5: Bezugsebene (Energie- oder Masseschicht)

- Schicht 6 (unterste Schicht): Bauteilmontage und Routing-Ebene

Dieser Lagenaufbau nutzt die Vorteile von 6-Lagen-Platinen voll aus und bietet vollständige Bezugsebenen und optimierte Rückwege für Hochgeschwindigkeitssignale.

Vergleich der drei wichtigsten Stackup-Lösungen

Je nach den Anforderungen der Anwendung gibt es bei 6-Lagen-Leiterplatten im Wesentlichen drei Aufbauprinzipien:

Lösung 1: Symmetrischer Aufbau (Vorrang der Signalebene)

Schicht 1: Signal (oben)

Schicht 2: Masse

Schicht 3: Signal

Schicht 4: Leistung

Schicht 5: Signal

Schicht 6: Masse (unten)Merkmale:

- Identische Bezugsebenenstruktur über und unter den mittleren Schichten

- Hervorragende Leistung bei der Signalintegrität

- Weit verbreitet in digitalen, analogen und gemischten RF-Designs

- Hohe Routingdichte, geeignet für komplexe Designs

Lösung 2: Asymmetrisches Layout (leistungsoptimiert)

Schicht 1: Signal (oben)

Schicht 2: Masse

Schicht 3: Signal

Schicht 4: Leistung

Schicht 5: Leistung

Schicht 6: Masse (unten)Merkmale:

- Ermöglicht die Aufteilung der Leistungsebene in mehrere Regionen

- Eine unterbrochene Grundplatte kann die Signalqualität beeinträchtigen

- Geeignet für Konstruktionen, die eine komplexe Stromverteilung erfordern

- Relativ geringere Kosten, aber etwas schlechtere EMC-Leistung

Lösung 3: Hybrides Layout (Priorität für Signalintegrität)

Schicht 1: Signal (oben)

Schicht 2: Masse

Schicht 3: Signal

Schicht 4: Masse

Schicht 5: Strom

Schicht 6: Masse (unten)Merkmale:

- Jede Signalebene hat eine benachbarte Referenzebene

- Enge Kopplung zwischen Energie- und Masseschichten

- Optimale Umgebung für die Übertragung von Hochgeschwindigkeitssignalen

- Verzicht auf einige Routing-Schichten für bessere SI-Leistung

Goldene Regeln des Stackup-Designs

- Nachbarschaft der Signalschicht zu Referenzebenen: Stellen Sie sicher, dass jede Signalebene über mindestens eine angrenzende vollständige Referenzebene (GND oder Power) verfügt, um niederohmige Rückleitungen für Hochgeschwindigkeitssignale zu gewährleisten.

- Power-Ground Plane Pairing-Prinzip: Ordnen Sie Leistungs- und Masselagen auf benachbarten Lagen an (typischerweise 0,1-0,2 mm Abstand), um eine natürliche Entkopplungskapazität zu bilden und Leistungsrauschen zu reduzieren.

- Symmetrisches Design: Halten Sie die Stapelsymmetrie so weit wie möglich aufrecht, um eine Verformung der Platine aufgrund ungleicher Wärmeausdehnungskoeffizienten zu vermeiden.

- Schutz der kritischen Signalschicht: Führen Sie die empfindlichsten Hochgeschwindigkeitssignale auf den inneren Lagen (Lagen 3/4) und nutzen Sie die äußeren Lagen zur natürlichen Abschirmung.

Profi-TippFür Hochgeschwindigkeitsdesigns im GHz-Bereich wird Solution 3 Stackup empfohlen. Zwar wird dabei eine Routing-Ebene geopfert, doch bietet sie optimale Signalintegrität und EMV-Leistung.

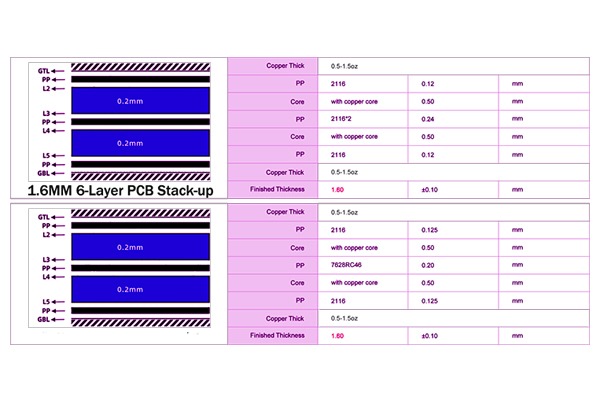

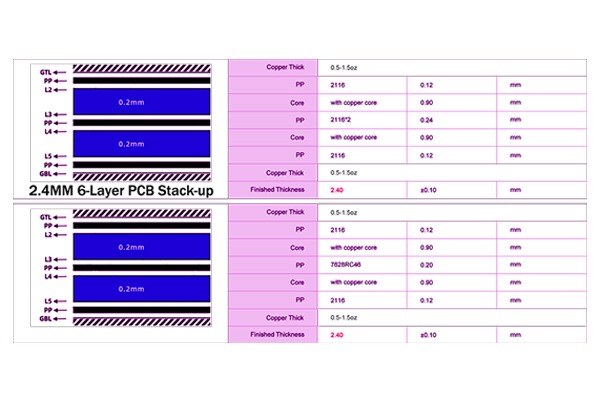

6-Lagen-PCB-Dickenberechnung und Materialauswahl

Die Gesamtdicke der Leiterplatte ist ein Parameter, der bereits in der Entwicklungsphase festgelegt werden muss und sich direkt auf die Auswahl der Steckverbinder, die mechanische Festigkeit und die Dicke des Endprodukts auswirkt.

Dicke Zusammensetzung Faktoren

Drei Hauptfaktoren bestimmen die Gesamtdicke der 6-Lagen-Leiterplatte:

- Kupferschichtdicke:

- Außenfolie: Typischerweise 1 oz (35 μm), 0,5 oz für Hochfrequenzanwendungen

- Innenfolie: 1 oz oder 0,5 oz (18 μm)

- Flugzeugschichten: Empfohlen werden 2 oz (70 μm) für eine höhere Strombelastbarkeit.

- Dielektrische Schichtdicke:

- Typische Werte: 8–14 mil (200–350 μm)/Schicht

- Werkstoffe: FR4, Hochgeschwindigkeitsmaterialien (z. B. Rogers, Isola)

- Dünnere Dielektrika tragen zur Verringerung des Übersprechens zwischen den Schichten bei

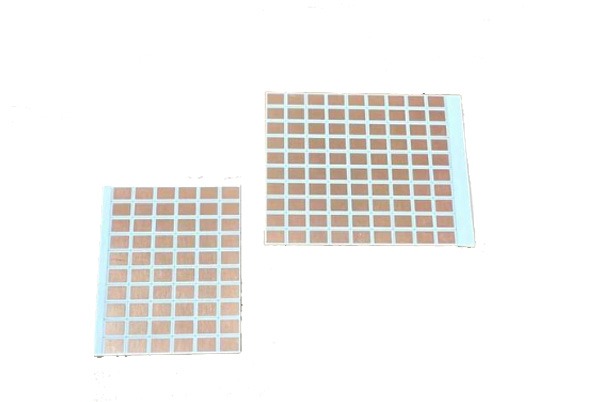

- Lamination Prozess:

- 2 Pressvorgänge: Zuerst werden die unteren 3 Lagen gepresst, dann die oberen 3 Lagen

- 3 Presszyklen:Jeweils 2 Schichten pressen für eine präzisere Dickenkontrolle zu höheren Kosten

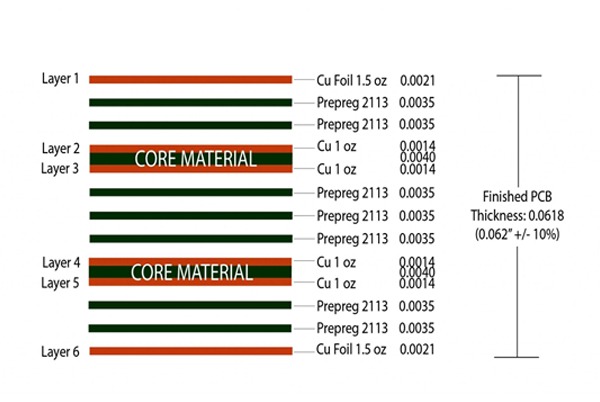

Typisches Beispiel für eine 6-Lagen-Plattendicke

Nachstehend finden Sie eine Dickenaufteilung für eine symmetrisch aufgebaute 6-Lagen-Leiterplatte:

| Ebene Typ | Dicke | Material Beschreibung |

|---|---|---|

| Schicht1 (oben) | 35 μm | 1oz Kupferfolie |

| Dielektrikum1 | 254 μm | FR4, 10mil |

| Schicht2 (GND) | 70 μm | 2oz Kupferfolie |

| Dielektrikum2 | 254 μm | FR4, 10mil |

| Schicht3 (Signal) | 35 μm | 1oz Kupferfolie |

| Dielektrikum3 | 508 μm | Kernplatte, 20mil |

| Schicht4 (Signal) | 35 μm | 1oz Kupferfolie |

| Dielektrikum4 | 254 μm | FR4, 10mil |

| Schicht5 (PWR) | 70 μm | 2oz Kupferfolie |

| Dielektrikum5 | 254 μm | FR4, 10mil |

| Schicht6 (Unten) | 35 μm | 1oz Kupferfolie |

| Gesamtdicke | 1,57 mm | ~62 Millionen |

Leitfaden zur Auswahl dielektrischer Materialien

Zu den üblichen dielektrischen Materialien für 6-Lagen-Leiterplatten gehören:

- Standard FR4:

- Bestes Kosten-Nutzen-Verhältnis

- Tg-Wert 130–140 °C

- Geeignet für die meisten Verbraucherprodukte

- Hochgeschwindigkeits-FR4 (z. B. Isola FR408, Panasonic Megtron6):

- Stabilere Dk/Df-Werte

- Geeignet für Signale im GHz-Bereich

- 30-50% höhere Kosten als Standard FR4

- Spezialisierte Materialien (z. B. Rogers RO4350B):

- Ultra-niedriger Verlust

- Für Anwendungen im Millimeterwellenbereich

- 5-10fache Kosten von FR4

Überlegungen zur Materialauswahl:

- Signalfrequenz: >5GHz empfiehlt Hochgeschwindigkeitsmaterialien

- Budget:Hochgeschwindigkeitsmaterialien erhöhen die Stücklistenkosten erheblich

- Thermische Leistung:Materialien mit hoher Tg eignen sich für Umgebungen mit hohen Temperaturen

- Schwierige Verarbeitung:Einige Hochfrequenzmaterialien erfordern spezielle Verfahren

Prozessablauf bei der Herstellung von 6-Lagen-Leiterplatten

Die Herstellung von 6-Lagen-Leiterplatten ist ein präziser und komplexer Prozess, der mehrere kritische Schritte umfasst:

1. Design und technische Vorbereitung

- Vollständiger Schaltplanentwurf und Layout-Routing

- Ermitteln des Lagenaufbaus und der Materialspezifikationen

- Durchführung von Design Rule Checks (DRC) und Signalintegritätsanalysen

- Generierung von Gerber-, Drill- und Netzlistendateien

Kernpunkt: Frühzeitige Kommunikation der Stapellösung mit dem Hersteller, um sicherzustellen, dass die Konstruktion mit den Möglichkeiten des Werks übereinstimmt.

2.Übertragung von Innenschichtmustern

- Reinigung von kupferbeschichtetem Laminat: Entfernen von Oberflächenoxiden und Verunreinigungen

- Trockenfilm-KaschierungAufbringen eines lichtempfindlichen Trockenfilms auf die Kupferoberfläche

- ExpositionÜbertragung der Schaltungsmuster auf die trockene Folie mit Laser oder Fotoplotter

- EntwicklungNicht belichtete trockene Filmbereiche auflösen

- ÄtzenUngeschütztes Kupfer entfernen

- Strippen: Entfernen Sie die restliche trockene Folie, um die innere Schicht zu bilden.

3.Lamination Prozess

- Ebenenausrichtung: Schichten in der Reihenfolge mit Prepreg dazwischen ausrichten

- Vorlaminierung: Anfängliche Bindung bei niedriger Temperatur und niedrigem Druck

- Heißpressen: Vollständige Aushärtung bei hoher Temperatur (180–200 °C) und hohem Druck

- Kühlung und Formgebung: Kontrolle der Abkühlgeschwindigkeit zur Vermeidung von Verformungen

4.Bohren und Metallisierung von Löchern

- Mechanisches BohrenBohren von Durchgangslöchern mit Hartmetallbohrern

- Entfärben: Harzreste von den Lochwänden entfernen

- Stromlose Kupferabscheidung: Eine 0,3–0,5 μm dicke Kupferschicht auf die Lochwände aufbringen.

- Galvanik: Verdicken Sie das Lochkupfer auf 25-30 μm.

5.Übertragung von Außenschichtmustern

Verfahren ähnlich wie bei den inneren Schichten, aber mit Anmerkung:

- Die äußere Folie ist dicker (normalerweise 1 Unze).

- Höhere Anforderungen an die Kontrolle von Linienbreite und Abstand

- Muss Lötmaskenöffnung und Oberflächenbeschaffenheit berücksichtigen

6.Oberflächenbehandlung und Endbearbeitung

- Anwendung der Lötmaske: Schutz der nicht zu lötenden Bereiche

- OberflächeZu den Optionen gehören HASL, ENIG, OSP, usw.

- SiebdruckHinzufügen von Bauteilkennzeichen und Markierungen

- Konturbearbeitung: Brettkanten fräsen, V-förmig ritzen

- Elektrische Prüfung: Unterbrechungs-/Kurzschlussprüfung und Impedanzprüfung

Techniken zur Optimierung der Signalintegrität

Die zentrale Herausforderung beim 6-Lagen-Leiterplattendesign besteht darin, die Integrität der Hochgeschwindigkeitssignale zu gewährleisten.Nachstehend finden Sie die wichtigsten Optimierungsstrategien:

1. Entwurf der Impedanzkontrolle

- Verwenden Sie Feldlöser-Tools (z. B. Polar SI9000) zur genauen Berechnung:

- Impedanz des Mikrostreifens (äußere Schicht)

- Impedanz der Streifenleitung (innere Schicht)

- Differenzielle Paarimpedanz

- Typische Impedanzwerte:

- Einseitig: 50 Ω

- Differential: 100 Ω (USB, PCIe usw.)

Design-Essentials:

- Konsistente Leiterbahnbreite beibehalten

- Vermeiden Sie rechtwinklige Kurven (verwenden Sie 45°-Kurven oder Rundungen).

- Differenzielle Paarlängen anpassen (Toleranz ±5 mil)

2.Optimierung der Energieintegrität

- PDN-Design mit niedriger Impedanz:

- Verwenden Sie dünne Dielektrika (3-4mil), um die Kopplung zwischen Leistung und Massefläche zu verbessern.

- Richtig platzierte Entkopplungskondensatoren (Kombination aus großen und kleinen Werten)

- Techniken der ebenen Segmentierung:

- Vermeiden Sie Signalspuren, die Splitbereiche kreuzen

- Sicherstellung einer ausreichenden Entkopplung für jeden Leistungsbereich

- Verwenden Sie “Insel” Segmentierung für empfindliche analoge Leistung

3.EMC-Design-Strategien

- Zwischenschicht-Abschirmung:

- Weiterleitung von Hochgeschwindigkeitssignalen auf inneren Schichten (Schichten 3/4)

- Äußere Masseflächen zur Abschirmung verwenden

- Randbehandlung:

- Platzieren Sie durchkontaktierte Löcher im Abstand von λ/20.

- Halten Sie empfindliche Signale von Platinenrändern fern (>3mm)

- Zonierung Layout:

- Streng getrennte digitale/analoge Bereiche

- Isolierung von Hochfrequenzkreisen

6-Lagen-Leiterplatte vs. 4-Lagen-Leiterplatte: Wie wählt man?

Wann sollte man eine 4-Lagen-Leiterplatte wählen?

- Entwürfe von mittlerer bis geringer Komplexität

- Kleinere Plattengröße (<150 cm²)

- Signalraten <1Gbps

- Kostensensible Projekte

- Nur 2-3 Hauptstromkreise

Wann auf 6-Lagen-Leiterplatten aufgerüstet werden sollte:

- Bedarf an hochdichten Verbindungen (z. B. BGA-Komponenten)

- Mehrere Stromversorgungssysteme (>3 Spannungsdomänen)

- Hochgeschwindigkeitssignale (>2Gbps)

- Designs mit gemischten Signalen (analog+digital+RF)

- Strenge EMC-Anforderungen

- Besseres Wärmemanagement erforderlich

Kostenvergleich6-Lagen-Leiterplatten kosten in der Regel 30-50 % mehr als 4-Lagen-Leiterplatten, aber durch ein optimiertes Stapeldesign kann die Größe der Leiterplatte reduziert werden, um die Kostensteigerung teilweise auszugleichen.

Professionelle Design-Empfehlungen und FAQ

Design-Checkliste

- Ist die Stapelsymmetrie sinnvoll?

- Hat jede Signalebene eine benachbarte Referenzebene?

- Ist der Abstand zwischen Stromversorgungsebene und Massefläche ausreichend klein?

- Vermeiden kritische Signale die Überquerung geteilter Bereiche?

- Stimmt die Impedanzberechnung mit dem Verfahren des Herstellers überein?

- Wurden Fertigungstoleranzen (±10 %) berücksichtigt?

Häufig gestellte Fragen

Q1: Wie wählt man dielektrische Materialien für 6-Lagen-Platten aus?

A1: Berücksichtigen Sie diese Faktoren:

- Signalfrequenz: Hohe Frequenz erfordert Materialien mit niedrigem Df

- Thermische Leistung:Materialien mit hoher Tg für Umgebungen mit hohen Temperaturen

- Haushalt:Hochgeschwindigkeitsmaterialien erhöhen die Kosten erheblich

- Schwierige Verarbeitung:Einige Materialien erfordern spezielle Verfahren

F2: Wie wird die Dicke der dielektrischen Schicht bestimmt?

A2: Entscheidung auf der Grundlage:

- Anforderungen an die Zielimpedanz

- Erforderliche Spannungsfestigkeit zwischen den Schichten

- Prozessfähigkeiten des Herstellers

- Grenzen der Gesamtdicke

- Anforderungen an die Signalisolierung

F3: Was sind die häufigsten Fehler beim Design von 6-Lagen-Leiterplatten?

A3: Zu den häufigsten Fehlern gehören:

- Diskontinuierliche Bezugsebenen

- Hochgeschwindigkeitssignale für geteilte Bereiche

- Übermäßiger Abstand zwischen Leistung und Massefläche

- Vernachlässigung der Rückweggestaltung

- Ungenaue Impedanzberechnungen

Professionell PCB-Herstellung Service-Empfehlung

Für 6-Lagen-Leiterplatten und mehr ist die Wahl eines erfahrenen Herstellers entscheidend. Wir empfehlen, Dienstleistungen mit in Betracht zu ziehen:

✅ Professionelle Mehrschichtplatinenfähigkeit (bis zu 30 Schichten)

✅ ±7 % Genauigkeit der Impedanzregelung

✅ Mehrere Oberflächenveredelungsoptionen (ENIG, OSP, Immersionssilber usw.)

✅ Kostenlose DFM-Prüfung und technische Unterstützung

✅ Schnelle Prototypenerstellung (innerhalb von nur 48 Stunden)

Sofortiges Angebot für die Herstellung von 6-Layer-PCBs anfordern: Ihre Anforderungen einreichen

Das Design von 6-Lagen-Leiterplatten ist eine komplexe technische Aufgabe, die eine umfassende Berücksichtigung von Signalintegrität, Leistungsintegrität, EMV-Leistung und Herstellungskosten erfordert. Durch ein vernünftiges Stapelschema (wie das empfohlene Schema 3), eine präzise Impedanzkontrolle und optimierte Routing-Strategien können die Leistungsvorteile von 6-Lagen-Leiterplatten voll ausgeschöpft werden.

Verwandte Beiträge