Dos fundamentos às estratégias avançadas para aplicações de IA e de alta velocidade

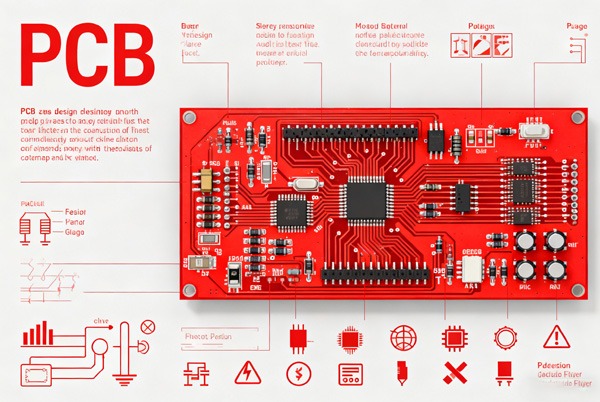

A placa de circuito impresso é o esqueleto e o sistema nervoso dos produtos electrónicos. A estabilidade e o desempenho de tudo, desde simples projectos de microcontroladores a complexos servidores de IA, estão profundamente enraizados na qualidade do design da placa de circuito impresso. Este guia, compilado pela equipa de peritos em engenharia da TOPFASTO livro, que é um guia completo desde os conceitos básicos até às estratégias avançadas.

Índice

Processo fundamental de design de PCB - Um ponto de partida robusto

Para os principiantes, seguir um processo de conceção normalizado é a chave do sucesso.

1: Preparação do projeto - Definição do esquema e das regras

- Desenho esquemático: Esta é a base lógica. Certifique-se de que os símbolos estão corretos, que as ligações são precisas e que atribui a cada componente a área de cobertura adequada.

- Planeamento de pré-layout: Comunicação precoce com o seu Fabricante de PCB (como TOPFAST) é fundamental. Obter os seus Documento de capacidade do processoA definição de parâmetros como a largura/espaçamento mínimo do traço, o tamanho mínimo do furo, a estrutura de empilhamento e a definição destes parâmetros como regras de conceção para evitar problemas de DFM desde o início.

2: Colocação de Componentes - O "Planeamento Urbano" de um Sistema Eletrónico

- Princípio fundamental: "A localização é tudo."

- Componentes críticos em primeiro lugar: Coloque primeiro o controlador principal (CPU/FPGA), a memória e os CIs de gestão de energia.

- Modularização funcional: Agrupar circuitos relacionados entre si (por exemplo, fonte de alimentação, circuito de relógio, secção analógica).

- Considerar a térmica e a montagem: Distribuir componentes de alta potência e planear percursos térmicos; colocar conectores e interruptores tendo em conta a mecânica do armário e a experiência do utilizador.

3: Roteamento - A arte e a ciência da conexão

- O poder em primeiro lugar: Encaminhar precocemente os traços de alimentação e de terra, assegurando que são curtos e largos para minimizar a impedância.

- Prioridade dos sinais críticos: Encaminhe relógios, pares diferenciais de alta velocidade e sinais analógicos sensíveis com os caminhos mais curtos e limpos.

- Regra 3W: Manter um espaçamento entre traços paralelos de pelo menos 3 vezes a largura do traço para reduzir a diafonia.

- Estratégia de ligação à terra: Normalmente, utiliza-se uma placa de terra dividida para as secções digitais e analógicas, ligadas num único ponto para evitar interferências de ruído.

4: Pós-processamento e criação de ficheiros de fabrico

- Controlo da RDC: Efetuar uma verificação final das regras de conceção para garantir que não existem omissões.

- Gerar ficheiros Gerber e Drill: Estes são os ficheiros padrão para a produção. Além disso, emite um ficheiro Lista de rede IPC-356 para testes de sondas de bordo para verificar se a conetividade eléctrica corresponde ao desenho.

- Comunicar com o fabricante: Fornecer uma Desenho de montagem e Requisitos do processo (por exemplo, acabamento da superfície - Ouro de imersão, HASLou ENIG?). Isto melhora a comunicação, assegurando um parceiro profissional como TOPFAST compreende com precisão as suas necessidades em matéria de "conceção para fabrico".

Dica TOPFAST: Para protótipos iniciais, recomendamos vivamente Teste elétrico (teste E) e Teste de sonda voadora. Esta é a linha de defesa final e mais económica contra potenciais curtos-circuitos ou aberturas.

Práticas avançadas - Filosofia de conceção para cenários de IA e alta velocidade

Quando o seu projeto entra na era dos GHz para placas aceleradoras de IA ou comutadores de alta velocidade, as regras básicas são apenas o ponto de partida. O sucesso depende da co-conceção de integridade e capacidade de fabrico.

1. Mudança de paradigma: Da "Interligação" à "Co-conceção de Sistemas"

Uma placa de circuito impresso moderna de alta velocidade é um complexo 3D que inclui linhas de transmissão de sinais, a rede complexa de distribuição de energia (PDN)e um sistema de gestão térmica preciso. O objetivo deixa de ser "alcançar a funcionalidade" e passa a ser otimizar o equilíbrio entre Integridade do sinal (SI), Integridade da energia (PI) e Integridade térmica.

2. A base crítica: DFM e Conceção da Fiabilidade em Colaboração com TOPFAST

- Controlo preciso da impedância: Não se trata apenas de cálculos da largura do traço. Confirme o materiais de base/impregnados com o seu fabricante. TOPFAST's a equipa de engenharia oferece serviços de aconselhamento de empilhamento e cálculo de impedância para garantir a coerência desde a conceção até ao produto acabado.

- Design avançado de via e perfuração posterior: Vias cegas e enterradas são essenciais para BGAs de alta densidade. Para sinais superiores a 10 Gbps, Perfuração traseira (Stub Removal) é um processo padrão para eliminar os efeitos de stub e garantir a integridade do sinal. Confirme as capacidades de tais processos avançados com TOPFAST durante a fase de conceção.

3. Conceção orientada para a simulação: "Prototipagem" no mundo virtual

O antigo ciclo "conceção-fabrico-teste-revisão" é dispendioso e lento. O fluxo de trabalho moderno deve ser um ciclo iterativo "simular-otimizar-resimular" processo.

- Co-simulação SI/PI: Analisar a impedância de todo o PDN. Otimizar a colocação do condensador de desacoplamento para garantir uma impedância extremamente baixa nos pinos de alimentação do chip.

- Simulação Electromagnética (EM) 3D: Utilize solucionadores 3D de onda completa para modelar com precisão o comportamento de conectores e vias complexos em amplas gamas de frequência.

Estudo de caso TOPFAST: No projeto de placa aceleradora de IA de um cliente, o protótipo inicial apresentava uma elevada taxa de erro de bits (BER) a 25 Gbps. Através da combinação de simulação de canal e Análise do processo PCB da TOPFASTNo início do ano, foi identificado que a perda dieléctrica (Df) de um laminado específico era superior ao esperado. Após TOPFAST's recomendação, o material foi mudado para M7NEum material de perda ultra-baixa, e o estilo de trama do vidro foi optimizado. Isto permitiu um funcionamento estável a 32 Gbps com um BER melhor que 1E-12, sem quaisquer alterações de design.

4. Projetar para o futuro: Parcerias com especialistas para tecnologia de ponta

A fronteira tecnológica está sempre a avançar. A preparação para os sistemas da próxima geração requer atenção a:

- Materiais de perda ultra-baixa: À medida que os débitos de dados se aproximam dos 112 Gbps PAM-4, a norma FR-4 torna-se insustentável devido a perdas.

- Co-conceção a nível do sistema: Modelar e analisar a placa de circuito impresso, os conectores e os cabos como um sistema único.

- Colaboração profunda com um parceiro como a TOPFAST: Desde a consulta de stack-up e a revisão DFM a meio do ciclo até à implementação de processos especializados (por exemplo, press-fit híbrido, rigid-flex), um parceiro de fabrico experiente fornece não só produtos, mas conhecimento e garantia contínuos da engenharia durante todo o percurso.

Conclusão

O design de PCB é uma viagem meticulosa da lógica à física, do virtual à realidade. Os engenheiros excepcionais são tanto cientistas que dominam os circuitos e os campos electromagnéticos, como profissionais que compreendem profundamente os materiais e os processos. A parceria com um fabricante profissional como a TOPFAST significa ter um aliado de engenharia presente durante todo o seu percurso - desde a conceção à produção em massa. Isto assegura que as suas ideias, quer sejam fundamentais ou de ponta, são transformadas em produtos estáveis e fiáveis com a mais alta qualidade e a mais rápida velocidade, garantindo a sua vantagem competitiva no mercado.

FAQ sobre conceção de PCB

A:Sintoma: Embora a impedância seja calculada durante o projeto, a placa acabada não cumpre os valores-alvo ou apresenta descontinuidades. Isso causa reflexão do sinal, fechamento do diagrama de olho e instabilidade do sistema, especialmente em sinais de alta velocidade (por exemplo, HDMI, USB3.0, PCIe).

Causa principal:

A conceção a estrutura de empilhamento não corresponde aos materiais efetivamente utilizados pelo fabricante (por exemplo, discrepâncias no tipo de núcleo/preparado ou na constante dieléctrica - Dk).

A largura do traço ou a espessura do dielétrico varia devido às tolerâncias de fabrico.

Plano de referência incompleto; os traços de sinal passam por cima de divisões (anti-pads) no plano.

Solução:

Contacte o seu fabricante (como a TOPFAST) desde o início: Obter e utilizar as recomendações do fabricante tabela de empilhamento e os parâmetros de cálculo da impedância antes da apresentação.

Anotação clara: Assinalar claramente quais são os traços impedância controlada, o seu valor-alvo e a camada de referência nos ficheiros Gerber e nas notas de fabrico.

Evitar os cruzamentos: Assegurar que os traços de sinal de alta velocidade têm um plano de referência sólido e contínuo por baixo.

A:Sintoma: Ondulação de tensão significativa nos pinos de alimentação do chip, levando a erros aleatórios do sistema, particularmente durante a comutação lógica de alta velocidade.

Causa principal:

Os condensadores de desacoplamento colocados demasiado longe dos pinos de alimentação do chip, introduzindo uma indutância parasita excessiva, tornam-nos ineficazes a altas frequências.

Utilização de valores ou tipos de condensadores inadequados (por exemplo, falta de condensadores de pequeno valor com boas caraterísticas de alta frequência).

O próprio caminho de alimentação é demasiado fino ou longo, apresentando uma impedância elevada.

Solução:

Princípio da "proximidade": Coloque condensadores de pequeno valor (por exemplo, 0,1 µF, 0,01 µF) o mais próximo possível dos pinos de alimentação do chip, dando prioridade ao caminho de retorno mais curto.

Otimizar Vias: Utilizar várias vias para ligações de alimentação/terra para reduzir a indutância.

Efetuar a análise PDN: Validar a estratégia de desacoplamento utilizando simulações de Integridade de Potência (PI), em vez de confiar apenas na experiência.

A:Sintoma: Incapacidade de encaminhar todos os sinais de chips BGA de elevada contagem de pinos (por exemplo, FPGAs, GPUs), ou ser forçado a adicionar muitas camadas de PCB apenas para o fan-out, aumentando significativamente o custo.

Causa principal:

Não utilização de todos os canais de encaminhamento disponíveis sob o BGA. Confiança apenas no tradicional "dog-bone" pad fan-out.

Desconhecimento das capacidades de microvia do fabricante, o que leva a evitar a tecnologia de via cega/enterrada.

Solução:

Utilizar a tecnologia Via-in-Pad (VIP): Colocar microvias perfuradas a laser diretamente nas almofadas BGA. Este é o método preferido para a conceção de BGA de alta densidade.

Consultar as capacidades de fabrico: Confirmar precisão de perfuração a laser e empilhados através de capacidades com a TOPFAST. Planear para HDI (Interligação de Alta Densidade) e vias cegas/enterradas no início da fase de conceção, o que permite frequentemente obter uma maior densidade de encaminhamento com menos camadas.

A:Sintoma: Os componentes de alta potência (por exemplo, processadores, circuitos integrados de potência) sobreaquecem sob carga, accionando a proteção térmica e provocando a limitação do desempenho ou a reinicialização do sistema.

Causa principal:

A conceção térmica da placa de circuito impresso é negligenciada. A confiança é colocada apenas no dissipador de calor do componente sem conduzir eficazmente o calor para a placa ou caixa.

Área de cobre insuficiente sob a pastilha para uma propagação eficaz do calor.

Falta de vias térmicas, ou estas estão insuficientemente preenchidas.

Solução:

Adicionar caminhos térmicos: Colocar um conjunto denso de vias termicamente preenchidas no padrão de terra da placa de circuito impresso sob o chip para transferir rapidamente o calor para o plano de terra/alimentação no lado oposto.

Aumentar a área de cobre: Atribuir maiores áreas de cobre nos planos internos (especialmente no solo) por baixo dos componentes de aquecimento para ajudar à dissipação do calor.

Utilizar uma folha de cobre mais espessa: Para áreas de alta corrente/alto calor, consulte a TOPFAST sobre a utilização de folhas de cobre pesadas (por exemplo, 2 oz).

A:Sintoma: O design funciona perfeitamente em simulação/protótipo, mas a produção de pequenos lotes sofre de baixo rendimento, ou ocorrem problemas como tombstoning, ponte de solda ou juntas frias durante a montagem SMT.

Causa principal:

Não cumprimento das regras básicas Conceção para a capacidade de fabrico (DFM) e Conceção para montagem (DFA) regras.

Má colocação de componentes (por exemplo, colocar QFPs de passo fino no lado da soldadura por onda).

Conceção incorrecta da abertura do estêncil.

Solução:

Respeitar as capacidades do processo: Assegurar que o espaçamento entre almofadas e a distância entre componentes cumprem os requisitos do equipamento SMT. Evitar colocar componentes sensíveis/pequenos na sombra de peças maiores durante a refusão ou em áreas de soldadura por onda.

Fornecer um ficheiro de centroide exato: Gerar um ficheiro correto ficheiro pick-and-place (ficheiro centroide) que contém o designador de referência, as coordenadas X/Y e a rotação, assegurando uma programação precisa da máquina.

Aproveitar a verificação DFM do fabricante: Submeter os ficheiros de projeto ao TOPFAST para uma análise DFM profissional antes da produção. Isto permite identificar atempadamente potenciais problemas, tais como uma má conceção das almofadas, armadilhas de ácido ou folga de montagem insuficiente, evitando novas rotações dispendiosas.