PCB Güvenilirliğini Geliştirmede Sık Karşılaşılan Sorunlar

İçindekiler

PCB Empedansı Nasıl Hesaplanır?

PCB empedansının hesaplanması, özellikle yüksek hızlı ve RF devreleri için sinyal bütünlüğünü sağlar.

1. PCB Yığınını ve Geometrisini Belirleyin

- Katman sayısı: Tek, çift veya çok katmanlı.

- İz genişliği (W) ve kalınlık (T): Empedans kontrolü için kritiktir.

- Dielektrik kalınlığı (H): Sinyal katmanı ile referans düzlemi (örn. toprak) arasındaki mesafe.

- Bakır ağırlığı: Tipik olarak 0,5 oz (17,5 µm) ila 2 oz (70 µm).

2. Dielektrik Sabitini (Dk ya da εkatı) tanımlayın

- FR-4: ~4.3-4.8 (frekansa göre değişir).

- Rogers RO4003C: ~3,38 (RF için düşük kayıplı).

- Poliimid: ~3.5 (esnek PCB'ler).

- Not: Dk daha yüksek frekanslarda hafifçe azalır.

3. Empedans Hesaplama Yöntemini Seçin

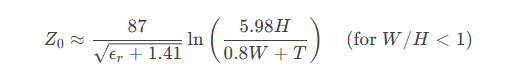

Mikroşerit (toprak düzlemi üzerinde dış katman izi):

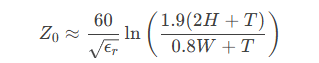

Stripline (iki toprak düzlemi arasındaki iç katman):

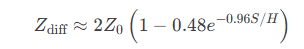

Diferansiyel Çift: İzler arasında boşluk (S) gerektirir.

4. Empedans Hesaplayıcıları veya Araçları Kullanın

- Çevrimiçi Araçlar: Saturn PCB Toolkit, EEWeb Hesaplayıcı.

- PCB Yazılımı: Altium Designer, KiCad veya Cadence yerleşik empedans hesaplayıcıları içerir.

- EM Simülatörleri: Ansys HFSS, CST (gelişmiş tasarımlar için).

5. Sonuçlara Göre Tasarımı Optimize Edin

- Ayarla iz genişliği (↑ genişlik → ↓ empedans).

- Değiştirmek dielektrik kalınlığı (↑ H → ↑ empedans).

- Tweak iz aralığı diferansiyel çiftler için.

- Seçiniz malzemeler uygun Dk ile (örneğin, RF için Rogers).

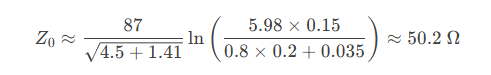

Örnek Hesaplama (FR-4 Mikroşerit)

Verildi:

- İz genişliği (W) = 0,2 mm

- Dielektrik kalınlığı (H) = 0,15 mm

- Bakır kalınlığı (T) = 0,035 mm

- εkatı = 4,5

Mikroşerit formülünü kullanarak:

RF sinyalleri için standart 50Ω empedansla eşleşir.

Sinyal bütünlüğü nasıl dikkate alınır? PCB tasarımı?

1. Yerleşim Tasarımı

PCB yerleşim tasarımında, sinyal hatlarının, güç hatlarının ve toprak hatlarının yerleşiminin dikkate alınması ve sinyal hatlarının, güç hatlarının ve toprak hatlarının kesişmesinden kaynaklanan parazitlerin önlenmesi önemlidir. Ek olarak, karışma ve gecikmeyi azaltmak için sinyal hatlarının uzunluğunu en aza indirmek esastır.

2. Empedans Eşleştirme

Yüksek hızlı sinyal hatları tasarlanırken, sinyal hatlarının empedansının sinyal kaynağı ve yükün empedansıyla eşleşmesini sağlamak ve böylece sinyal yansıması ve karışma olmasını önlemek için empedans eşleştirmesi yapılmalıdır.

3. Sinyal Hattı Yönlendirme

PCB tasarımında, sinyal hatlarının yönlendirilmesi de sinyal bütünlüğünü etkiler ve belirli kurallara uymalıdır. Örneğin, diferansiyel sinyal hatları belirli bir aralığı korumalı ve paralel olarak yönlendirilmeli, tek uçlu sinyal hatları toprak hatlarına paralel olarak yönlendirilmeli ve sinyal hattı bükülmeleri en aza indirilmelidir.

4. Güç ve Topraklama

PCB tasarımında, güç ve topraklama tasarımı da sinyal bütünlüğünü etkiler. Kararlı güç ve topraklama kullanılmalı ve güç ve topraklamanın direnci ve endüktansı mümkün olduğunca en aza indirilmelidir.

5. Simülasyon Doğrulaması

PCB tasarımı tamamlandıktan sonra, sinyal bütünlüğünün gereksinimleri karşıladığından emin olmak için simülasyon doğrulaması gereklidir. Simülasyon sayesinde sinyal gecikmesi, yansıma ve karışma gibi sorunlar tespit edilebilir ve PCB tasarımı optimize edilebilir.

PCB Tasarımında Elektromanyetik Uyumluluk (EMC) Nasıl Dikkate Alınır?

1. EMC için PCB Düzeni

- Paralel Yönlendirmeyi En Aza İndirin: Karışma ve elektromanyetik kuplajı azaltmak için sinyal ve güç/toprak hatları arasında uzun paralel çalışmalardan kaçının.

- Kritik Sinyal İzolasyonu: Yüksek hızlı (örn. saatler, RF) ve hassas analog sinyalleri gürültülü devrelerden (örn. anahtarlamalı güç kaynakları) ayırın.

- Katman Yığma Stratejisi:

- Ekranlama sağlamak için sinyal katmanlarına bitişik sağlam toprak düzlemleri kullanın.

- Yüksek hızlı sinyalleri, muhafaza için toprak düzlemleri arasındaki iç katmanlara yönlendirin.

2. Topraklama Teknikleri

- Düşük Empedanslı Zemin Düzlemleri: Toprak döngülerini en aza indirmek ve yayılan emisyonları azaltmak için kesintisiz toprak düzlemleri kullanın.

- Zeminleri Dikkatlice Bölün: Analog/dijital topraklamaları yalnızca gerektiğinde tek bir bağlantı noktasıyla (örn. ferrit boncuk veya 0Ω direnç) ayırın.

- Stitching aracılığıyla: Boşluk rezonanslarını bastırmak için yüksek frekanslı izlerin veya kart kenarlarının etrafına birden fazla topraklama yolu yerleştirin.

3. Filtreleme ve Bastırma

- Ferrit Boncuklar: Yüksek frekanslı gürültüyü engellemek için güç/IO hatlarına ekleyin.

- Dekuplaj Kondansatörleri: Yüksek ve orta frekanslı gürültüyü filtrelemek için IC güç pinlerinin yakınına yerleştirin (örneğin, 0.1μF + 1μF).

- Ortak Mod Şokları: Ortak mod radyasyonunu bastırmak için diferansiyel çiftlerde (örn. USB, Ethernet) kullanın.

4. Ekranlama ve Arayüz Tasarımı

- Kablo Ekranlama: Şasiye 360° topraklamalı blendajlı konektörler (örn. USB, HDMI) kullanın.

- Pano Seviyesi Ekranlama: Hassas RF devrelerinin üzerine metal kutular veya iletken kaplamalar ekleyin.

- Kenar Koruma: Hassas izleri kart kenarlarından uzağa yönlendirin; koruma izleri kullanın veya etraflarına topraklanmış bakır dökün.

5. Simülasyon ve Test

- Layout Öncesi Analiz: Radyasyon sıcak noktalarını modellemek için ANSYS HFSS veya CST gibi araçları kullanın.

- Post-Layout Doğrulama:

- Emisyon kaynaklarını belirlemek için yakın alan taramaları gerçekleştirin.

- Yayılan/iletilen emisyonlar için uyumluluk testi (örn. FCC, CE) gerçekleştirin.

- Tasarım Yinelemesi: Test sonuçlarına göre optimize edin (örneğin, sonlandırma dirençleri ekleyerek veya iz aralığını ayarlayarak).

Örnek Düzeltmeler:

- 100MHz'lik bir saat aşırı derecede yayılıyor: Seri sonlandırma dirençleri ekleyin veya toprak düzlemleri arasında yönlendirin.

- Anahtarlama güç kaynağı gürültüsü: Giriş/çıkışta π-filtreleri (LC) uygulayın.

Bu uygulamaları entegre ederek, PCB'ler EMC standartlarını (örn. IEC 61000) karşılayabilir ve maliyetli yeniden tasarımları en aza indirebilir. Her zaman erken prototipleyin ve test edin!

PCB Tasarımında Güç Bütünlüğü (PI) Nasıl Dikkate Alınır?

1. Güç İzi Düzeni

- Kısa ve Geniş İzler: Gerilim düşüşünü ve gürültüyü azaltmak için direnci (R) ve parazitik endüktansı (L) en aza indirin.

- Sinyal İzleri ile Paralel Yönlendirmeden Kaçının: Güç gürültüsünün hassas sinyallere (örn. saatler, analog devreler) bağlanmasını önleyin.

- Katman Stratejisi:

- Çok katmanlı panolarda, tüm katmanları güç ve toprak düzlemlerine ayırın.

- Kritik güç rayları (örneğin, CPU çekirdek voltajı) özel güç düzlemlerine sahip olmalıdır.

2. Güç Filtreleme

- Dekuplaj Kondansatörleri:

- Voltajı stabilize etmek için güç girişlerinde yığın elektrolitik kapasitörler (10-100μF).

- Yüksek frekanslı gürültüyü filtrelemek için IC pinlerinin yakınında küçük seramik kapasitörler (0.1μF).

- LC Filtreler:

- Gürültüye duyarlı modüller (örn. PLL'ler) için π filtreleri (kapasitör + indüktör) ekleyin.

3. Güç ve Topraklama

- Düşük Empedanslı Dönüş Yolları:

- Sağlam toprak düzlemleri kullanın; empedans süreksizliklerine neden olan bölünmelerden kaçının.

- Güç/toprak düzlemlerini bağlamak için çoklu vialar (via endüktansını azaltır).

- Yıldız Topraklama:

- Tek noktadan topraklama ile yüksek güçlü ve hassas devreleri ayırın.

4. Simülasyon ve Doğrulama

- PDN (Güç Dağıtım Ağı) Analizi:

- Hedef empedans: ( Z_{\text{target}} = \frac{\Delta V}{\Delta I} ).

- Araçlar: ANSYS SIwave, Cadence Sigrity.

- Dalgalanma ve Gürültü Testi:

- Osiloskoplar veya simülasyonlarla güç gürültüsü seviyelerini doğrulayın.

Test Edilebilirlik için Tasarım (DFT) PCB Tasarımına Nasıl Dahil Edilir?

1. Test Noktaları ve Arayüzler

- Kritik Sinyal Test Noktaları:

- Prob erişimi için vialar veya pedler (çap ≥1mm, aralık ≥2,54mm) sağlayın.

- Test noktalarını etiketleyin (örn. TP1, TP2).

- Standart Arayüzler:

- JTAG, UART veya SWD arayüzlerini kart kenarlarına yakın yerleştirin.

2. Pano Etiketleme (Serigrafi)

- Bileşen İşaretleri:

- Referans belirleyicileri (örn. R1, C2), polariteyi (+/-) ve Pin 1'i etiketleyin.

- Yüksek kontrastlı serigrafi (beyaz/siyah) kullanın.

- Fonksiyonel Bölgeler:

- Kolay tanımlama için alanları (örneğin, "Güç Bölümü") ana hatlarıyla belirtin.

3. Programlanabilir Test Teknikleri

- Sınır Taraması (JTAG):

- IEEE 1149.1 uyumlu IC'ler (örn. FPGA'lar, MCU'lar) ara bağlantı testine olanak sağlar.

- Otomatik Test Ekipmanı (ATE):

- Yedek test fikstürü arayüzleri (örneğin, pogo pin pedleri).

4. Simülasyon ve Doğrulama

- DFT Kural Kontrolleri:

- Test noktası kapsamını sağlayın (örneğin, erişilebilir ağların >90%'si).

- Hata Modu Analizi:

- SPICE simülasyonları aracılığıyla test devrelerini doğrulayın.

Temel Tasarım İlkeleri Karşılaştırması

| Güç Bütünlüğü (PI) | Test Edilebilirlik için Tasarım (DFT) |

|---|---|

| Düşük empedanslı güç dağıtımı | Fiziksel test noktası erişilebilirliği |

| Dekuplaj kondansatörü optimizasyonu | JTAG/boundary tarama desteği |

| Güç-sinyal kuplajını en aza indirin | Açık bileşen/arayüz etiketlemesi |

| PDN simülasyonu ve dalgalanma analizi | ATE uyumlu tasarım |

Örnekler:

- PI Optimizasyonu: Çoklu 0805 0.1μF kapaklı DDR4 bellek güç düzlemleri (hedef empedans ≤0.1Ω).

- DFT Uygulaması: Otomatik uçan prob testi için 20 test noktasına sahip endüstriyel kontrol panosu.

Tasarımcılar PI ve DFT'yi sistematik olarak ele alarak güç performansını, test verimliliğini ve üretim güvenilirliğini artırabilir.

İlgili Yazılar