Prozessablauf bei der PCB-Herstellung

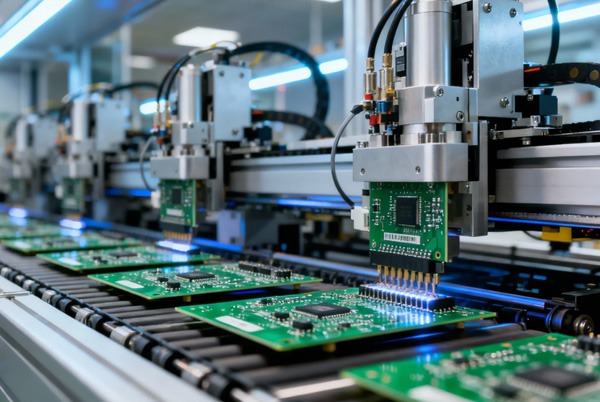

In der heutigen Welt, in der elektronische Geräte allgegenwärtig sind, dienen PCBs (Printed Circuit Boards) als das Skelett und Nervensystem elektronischer Produkte, wobei sich ihre Herstellungsprozesse direkt auf die Leistung und Zuverlässigkeit der Produkte auswirken. Ganz gleich, ob Sie Elektronikingenieur, Beschaffungsspezialist oder einfach nur an der Leiterplattenherstellung interessiert sind, ein Verständnis des gesamten Arbeitsablaufs bei der Herstellung von Leiterplatten ist unerlässlich. Dieser Artikel führt Sie durch jeden kritischen Schritt der Leiterplattenproduktion, vom Rohmaterial bis zum fertigen Produkt, und geht dabei auf die häufigsten Herausforderungen bei der Herstellung ein.

Inhaltsübersicht

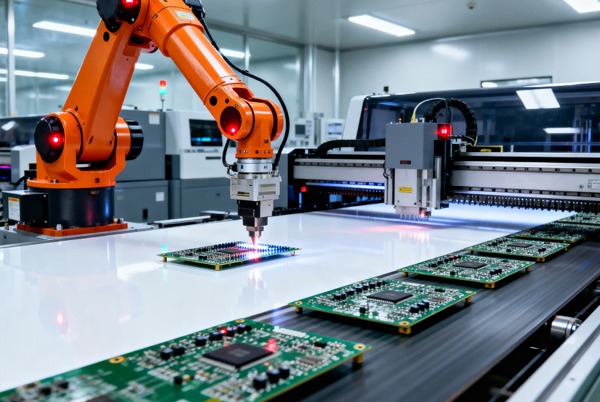

Detaillierte Aufschlüsselung des Kerns PCB-Herstellung Prozesse

1. Plattenschneiden (CUT): Der Ausgangspunkt für Präzision

Das Schneiden der Leiterplatten ist der erste Schritt in der Leiterplattenherstellung und bildet die Grundlage für die nachfolgenden Prozesse. Obwohl er scheinbar einfach ist, beinhaltet er mehrere technische Überlegungen:

- Auswahl des Materials:Zu den gängigen kupferkaschierten Laminatmaterialien gehören FR-4 (Glasfaserepoxid), Aluminiumsubstrate und Hochfrequenzmaterialien (z. B. Rogers), die jeweils unterschiedliche Schneideparameter erfordern.

- Abmessungskontrolle: Präziser Zuschnitt nach Designvorgaben für die Abmessungen UNIT (Einzelschaltung), SET (Panelized Array) und PANEL (Produktionspanel)

- Genauigkeitsanforderungen: Die moderne Leiterplattenherstellung erfordert in der Regel Schnitttoleranzen von ±0,10 mm.

- Randbehandlung: Schnittkanten müssen entgratet werden, um zu verhindern, dass raue Kanten die nachfolgenden Prozesse beeinträchtigen

Wichtige Überlegungen:

- Überprüfen Sie vor dem Schneiden den Materialtyp, die Dicke und das Kupfergewicht.

- Berücksichtigen Sie bei der Bestimmung der Plattengröße die Ausdehnung/Kontraktion des Materials in nachfolgenden Prozessen.

- Aufrechterhaltung einer sauberen Arbeitsumgebung zur Vermeidung von Oberflächenverschmutzung

- Lagern Sie verschiedene Materialien getrennt, um eine Vermischung zu vermeiden.

2.Inner Layer Dry Film Imaging:Präzise Schaltkreismuster erstellen

Das Innenschicht-Trockenfilmverfahren ist entscheidend für die genaue Übertragung von Designmustern auf Leiterplattensubstrate und besteht aus mehreren Teilprozessen:

Oberflächenvorbereitung (Panel Scrubbing)

- Kombiniert chemische Reinigung mit mechanischer Abrasion

- Entfernt Oxidation und schafft Mikrorauigkeit für bessere Trockenfilmhaftung

- Typische Parameter: 5-10mm Scheuerstellen, Ra 0,3-0,5μm Rauheit

Trockenfilm-Kaschierung

- Verbindet den lichtempfindlichen Trockenfilm thermisch mit der Kupferoberfläche

- Temperaturkontrolle: Normalerweise 100-120°C

- Druckregelung:Ungefähr 0,4-0,6MPa

- Geschwindigkeitskontrolle: 1,0-1,5m/min

Exposition

- Verwendet UV-Licht (365nm Wellenlänge) zur selektiven Aushärtung von Trockenfilm durch Phototool

- Energiekontrolle: 5-10mJ/cm²

- Genauigkeit der Registrierung: Innerhalb ±25μm

Entwicklung

- Verwendet 1%ige Natriumkarbonatlösung zum Auflösen von nicht ausgehärtetem Trockenfilm

- Temperaturregelung: 28-32°C

- Sprühdruck: 1,5- 2,5 bar

Ätzen

- Verwendet saure Kupferchloridlösung (CuCl2+HCl) zum Auflösen von freiliegendem Kupfer

- Ätzfaktor (Seitenätzkontrolle) >3,0

- Gleichmäßigkeit der Kupferdicke innerhalb von ±10%

Strip

- Verwendet 3-5%ige Natriumhydroxidlösung zur Entfernung des trockenen Schutzfilms

- Temperaturregelung: 45-55°C

- Zeitkontrolle: 60-90 Sekunden

Design-Empfehlungen:

- Mindestspur der Innenschicht ≥ 3 mil (0,075 mm)

- Vermeiden Sie isolierte Kupfermerkmale, um eine Überätzung zu verhindern.

- Verteilen Sie das Kupfer gleichmäßig, um einen Verzug der Laminierung zu verhindern.

- Entwurfsspielraum für kritische Signalbahnen hinzufügen

3. Behandlung mit braunem Oxid: Verbesserung der Zwischenschichthaftung

Die Behandlung mit braunem Oxid ist für die Herstellung mehrlagiger Leiterplatten von entscheidender Bedeutung, da sie in erster Linie die Haftung zwischen der inneren Kupferschicht und dem Prepreg (PP) verbessert:

- Chemische Reaktion: Bildet eine mikroraue organisch-metallische Komplexschicht auf der Kupferoberfläche

- Prozesskontrolle:

- Temperatur: 30-40°C

- Zeit: 1,5-3 Minuten

- Erhöhung der Kupferdicke: 0,3-0,8μm

- Überprüfung der Qualität:

- Gleichmäßigkeit der Farbe

- Wasserkontaktwinkeltest (sollte ≥30° sein)

- Prüfung der Schälfestigkeit (≥1,0N/mm)

Gemeinsame Probleme:

- Unzureichende Behandlung kann zu Delamination nach der Laminierung führen

- Eine Überbehandlung führt zu übermäßiger Rauheit und beeinträchtigt die Signalintegrität

- Die verarbeiteten Platten sollten innerhalb von 8 Stunden laminiert werden.

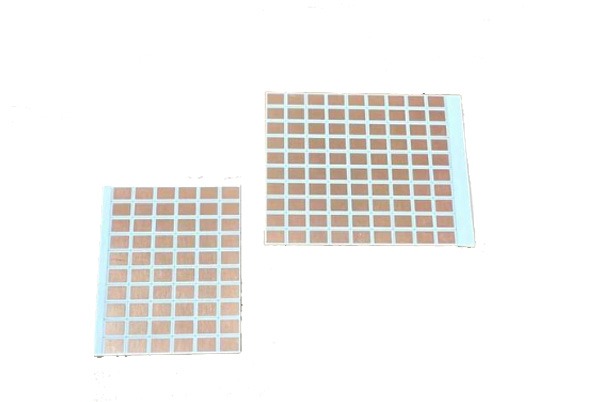

4.Kaschieren:Bildung von Mehrschichtstrukturen

Beim Laminieren werden mehrere Innenschichtkerne mit Prepreg (PP) unter Hitze und Druck zu mehrschichtigen Strukturen verbunden:

- Vorbereitung des Materials:

- Kupferfolie (normalerweise 1/3 oz oder 1/2 oz)

- Prepreg (z. B. die Sorten 1080, 2116, 7628)

- Edelstahlplatten, Kraftpapier und andere Hilfsmaterialien

- Prozess-Parameter:

- Temperatur: 170-190°C

- Druck: 15-25kg/cm²

- Zeit: 90-180 Minuten (je nach Brettstärke und Struktur)

- Kritische Kontrollen:

- Aufheizgeschwindigkeit: 2-3°C/min

- Abkühlungsrate: 1-2°C/min

- Vakuumniveau: ≤100mbar

Überlegungen zur Gestaltung:

- Beibehaltung der symmetrischen Stapelung (z. B. 8-Lagen-Platte: 1-2-3-4-4-3-2-1)

- Richten Sie die Leiterbahnen benachbarter Schichten rechtwinklig aus (z. B. horizontal auf einer Schicht, vertikal auf der benachbarten)

- Verwenden Sie PP mit hohem Harzgehalt für schwere Kupferplatten

- Berücksichtigen Sie den Materialfluss während des Laminierens bei Blind-/Buried-Via-Designs

5.Bohren:Herstellung von Präzisions-Verbindungen

Durch das Bohren werden vertikale Verbindungen zwischen den Leiterplattenschichten hergestellt, wobei die moderne Technologie eine außergewöhnliche Genauigkeit erreicht:

- Bohrer-Typen:

- Mechanisches Bohren (für Löcher ≥0,15mm)

- Laserbohren (für Microvias und Blind Vias)

- Typische Parameter:

- Spindeldrehzahl: 80.000-150.000 RPM

- Vorschubgeschwindigkeit: 1,5-4,0m/min

- Rückzugsgeschwindigkeit:10-20m/min

- Qualitätsstandards:

- Rauheit der Bohrlochwand ≤25μm

- Genauigkeit der Bohrlochposition ±0,05 mm

- Kein Nagelkopf oder Grat

Fehlersuche bei allgemeinen Problemen:

- Raue Lochwände: Optimieren Sie die Bohrparameter, verwenden Sie geeignetes Einführungs-/Backup-Material

- Verstopfte Löcher: Verbesserung der Spanabfuhr, Anpassung der Bohrreihenfolge

- Kaputte Bohrer: Überprüfung der Bohrqualität, Optimierung der Vorschubgeschwindigkeit

6.Stromlose Kupferabscheidung (PTH):Metallisierung von kritischen Löchern

Die stromlose Kupferabscheidung erzeugt leitende Schichten auf nicht leitenden Lochwänden, die für die Zuverlässigkeit von Leiterplatten entscheidend sind:

PTH-Prozessablauf

- Abschmieren: Entfernt Harzrückstände vom Bohren

- Chemisch Kupfer:

- Eine alkalische Lösung mit Formaldehyd als Reduktionsmittel

- Temperatur: 25-32°C

- Zeit: 15-25 Minuten

- Dicke des Kupfers: 0,3-0,8μm

- Paneelbeschichtung:

- Saure Kupfersulfatlösung

- Stromdichte: 1,5- 2,5ASD

- Dauer: 30-45 Minuten

- Dicke des Kupfers: 5-8μm

Qualitätsanforderungen:

- Prüfung der Hintergrundbeleuchtung ≥9 Stufen (≥90% Lochwandabdeckung)

- Thermischer Belastungstest (288°C, 10 Sekunden) ohne Delamination oder Blasenbildung

- Bohrlochwiderstand ≤300μΩ/cm

7. Übertragung von Außenschichtmustern

Ähnlich wie bei der Innenschichtabbildung, jedoch mit zusätzlichen Beschichtungsschritten:

- Oberfläche vorbereiten: Reinigung, Mikroätzung (entfernt 0,5-1μm Kupfer)

- Trockenfilm-KaschierungVerwendung von platingfestem Trockenfilm

- ExpositionVerwendet LDI (Laser Direct Imaging) oder herkömmliche Fototools

- EntwicklungErzeugt ein Beschichtungsmuster

- Musterbeschichtung:

- Dicke des Kupfers: 20-25μm (insgesamt)

- Zinndicke: 3-5μm (als Ätzresist)

- Strip:Entfernt Galvanisierungsresist

- ÄtzenEntfernt unerwünschtes Kupfer

Technische Höhepunkte:

- Kompensation der Leiterbahnbreite: Anpassung der Entwurfsbreite auf der Grundlage der Kupferdicke (in der Regel 10-20 % mehr)

- Gleichmäßigkeit der Beschichtung:Verwenden Sie eine Lösung mit hoher Streukraft und eine geeignete Anodenkonfiguration

- Kontrolle der Seitenätzung:Optimieren Sie die Ätzparameter, um die Genauigkeit der Leiterbahnbreite zu erhalten

8.Lötstoppmaske: Schaltungsschutzschicht

Die Lötstoppmaske schützt die Schaltkreise und beeinflusst die Qualität und das Aussehen des Lots:

- Anwendungsmethoden:

- Siebdruck: Für geringe Präzisionsanforderungen

- Sprühbeschichtung:Für unregelmäßige Kartonformen

- Vorhangbeschichtung:Hohe Effizienz, hervorragende Gleichmäßigkeit

- Prozessablauf:

- Oberflächenvorbereitung (Reinigung, Aufrauen)

- Aufbringen der Lötmaske

- Vorbacken (75°C, 20-30 Minuten)

- Belichtung (300-500mJ/cm²)

- Entwicklung (1%ige Natriumcarbonatlösung)

- Endgültige Aushärtung (150°C, 30-60 Minuten)

- Qualitätsstandards:

- Härte ≥6H (Bleistifthärte)

- Haftung: 100 % mit 3M-Klebebandtest bestanden

- Lötbeständigkeit: 288°C, 10 Sekunden, 3 Zyklen ohne Fehler

Gestaltungsrichtlinien:

- Minimale Lötmaskenbrücke ≥0,1mm

- BGA-Flächenöffnungen: 0,05 mm größer als Pads pro Seite

- Goldfinger erfordern eine Lötmaskenabdeckung

9.Oberflächenbeschaffenheit: Gleichgewicht zwischen Lötbarkeit und Dauerhaftigkeit

Verschiedene Oberflächen eignen sich für unterschiedliche Anwendungen:

| Ausführung Typ | Dickenbereich | Vorteile | Benachteiligungen | Typische Anwendungen |

|---|---|---|---|---|

| HASL | 1-25μm | Geringe Kosten, hervorragende Lötbarkeit | Schlechte Ebenheit, nicht für feines Pech geeignet | Unterhaltungselektronik |

| ENIG | Ni3-5μm/Au0,05-0,1μm | Ausgezeichnete Ebenheit, lange Lagerfähigkeit | Hohe Kosten, Risiko einer schwarzen Null | Hochzuverlässige Produkte |

| OSP | 0,2-0,5μm | Niedrige Kosten, einfaches Verfahren | Kurze Haltbarkeitsdauer (6 Monate) | Hochvolumige Unterhaltungselektronik |

| Imm Ag | 0,1-0,3μm | Gute Lötbarkeit, moderate Kosten | Anfälligkeit für Anlaufen, spezielle Verpackung ist erforderlich | RF/Hochfrequenz-Schaltungen |

| ENEPIG | Ni3-5μm/Pd0.05-0.1μm/Au0.03-0.05μm | Kompatibel mit verschiedenen Montagemethoden | Höchste Kosten | Fortschrittliche Verpackung |

Auswahlhilfe:

- Standard-Unterhaltungselektronik: HASL oder OSP

- Hochzuverlässige Produkte:ENIG

- Hochgeschwindigkeitsschaltungen:Imm Ag oder OSP

- Kantenverbinder:Hartvergoldung (1-3μm)

10.Fräsen: Präzise Umrissfertigung

Bei der Bearbeitung von Leiterplattenumrissen werden hauptsächlich drei Methoden angewandt:

- CNC-Fräsen:

- Genauigkeit: ±0,10 mm

- Mindestschlitzbreite: 1,0 mm

- Eckenradius: ≥0,5mm

- V-Scoring:

- Winkel: 30° oder 45°

- Verbleibende Dicke: 1/3 der Plattendicke (normalerweise 0,3-0,5 mm)

- Positionsgenauigkeit: ±0,10 mm

- Laserschneiden:

- Genauigkeit: ±0,05 mm

- Minimaler Schnittspalt: 0,2 mm

- Keine mechanische Belastung

Gestaltungsregeln:

- Halten Sie einen Abstand von ≥0,3 mm zwischen der Leiterplattenkante und den Schaltkreisen ein.

- Abtrennbare Laschen oder Mausbisse für verkleidete Designs

- Bereitstellung präziser DXF-Dateien für unregelmäßige Umrisse

- Abgeschrägte Kanten (typischerweise 20-45°) für Goldfingerboards

11.Elektrische Prüfung:Endgültige Qualitätsprüfung

Die Prüfung von Leiterplatten gewährleistet Funktionssicherheit:

- Testmethoden:

- Fliegende Sonde: Geeignet für die Produktion von Kleinserien mit hohem Mischungsverhältnis

- Prüfung von Vorrichtungen:Für die Großserienproduktion

- AOI (Automatisierte optische Inspektion):Ergänzende Prüfung

- Testabdeckung:

- 100%ige Nettokontinuität

- Isolationsprüfung (typischerweise 500V DC)

- Impedanzprüfung (für Platten mit kontrollierter Impedanz)

Gemeinsame Problemlösung:

- Öffnet: Falsche Öffnungen überprüfen (schlechter Kontakt der Prüfspitze)

- Kurze Hosen:Analyse der Lage des Kurzschlusses, Prüfung von Designfragen

- Impedanzabweichung:Überprüfung der Materialparameter und der Leiterbahnbreitenkontrolle

12.Endkontrolle & Verpackung

Der letzte Schritt der Qualitätsprüfung:

- Inspektionsgegenstände:

- Visuell: Kratzer, Flecken, Lötmaskenfehler

- Dimensionen: Dicke, Umriss, Lochgrößen

- Markierung:Legendenklarheit und Positionsgenauigkeit

- Funktionell:Qualität der Goldfingerbeschichtung, Impedanztests

- Verpackungsmethoden:

- Vakuumverpackung (Antioxidationsmittel)

- Antistatische Verpackung (für empfindliche Komponenten)

- Interleaved-Papier (verhindert Oberflächenkratzer)

- Kundenspezifische Trays (für hochpräzise Platten)

Versandstandards:

- IPC-A-600G Klasse 2 (kommerziell)

- IPC-A-600G Klasse 3 (hohe Zuverlässigkeit)

- Kundenspezifische Anforderungen

PCB-Herstellung FAQ (Q&A)

Q1: Warum blättert das Kupfer auf meiner Leiterplatte nach dem Löten ab?

Grundlegende Ursachen:

- Schlechte Haftung von Kupfer auf dem Substrat (Materialproblem)

- Überhöhte Löttemperatur oder -dauer

- Schlechtes Design (z. B. große Kupferfläche, die über dünne Leiterbahnen verbunden ist)

- Unzureichende Behandlung von Braunoxid

Lösungen:

- Wählen Sie hochwertige Laminatmaterialien

- Optimieren der Lötparameter (<260°C, <5 Sekunden)

- Verwendung von thermisch entlasteten Verbindungen in Konstruktionen

- Überprüfen Sie die Parameter des Braunoxidprozesses mit dem Hersteller

- Führen Sie bei Bedarf einen thermischen Belastungstest durch (288°C, 10 Sekunden, 3 Zyklen)

F2: Wie kann man bei mehrlagigen Leiterplatten die Fehlregistrierung von Lage zu Lage beheben?

Fehlregistrierung Quellen:

- Unstimmigkeiten bei der Expansion/Kontraktion von Materialien

- Lagenverschiebung beim Laminieren

- Unzureichende Genauigkeit der Belichtungsregistrierung

- Abweichungen von der Bohrposition

Verbesserungsmaßnahmen:

- Entwurfsphase:

- Registrierungsziele hinzufügen (mindestens 3)

- Gleichmäßige Kupferverteilung aufrechterhalten

- Berücksichtigung von Materialeigenschaften (spezielle Handhabung für Hochfrequenzmaterialien)

- Herstellung:

- Verwendung hochpräziser LDI-Belichtungsgeräte

- Implementierung einer Röntgenbohrungsausrichtung

- Anwendung von Algorithmen zur Kompensation von Materialschwund

- Sequentielle Laminierung für Platten mit hohem Aspektverhältnis in Betracht ziehen

- Auswahl der Materialien:

- Verwendung von Materialien mit niedrigem CTE-Wert

- Wählen Sie ein maßhaltiges Prepreg

F3: Wie können raue Lochwände in kleinen Löchern (<0,2mm) gelöst werden?

Technische Lösungen:

- Auswahl des Bohrers:

- Spezialbohrer (z. B. UC-Typ)

- Spitzenwinkel 130-140°

- Spiralwinkel 35-40°

- Optimierung der Parameter:

- Drehzahl auf 120.000-150.000 erhöhen

- Reduzieren Sie die Vorschubgeschwindigkeit auf 1,0-1,5m/min

- Wechseln Sie die Bohrer alle 500 Treffer

- Hilfsmittel:

- Hochdichtes Aluminium-Eingangsmaterial

- Spezielle Sicherungsplatten (z. B. Phenolharz)

- Nachbearbeitung:

- Verbesserte Abschmierung (Plasmabehandlung optional)

- Optimierung der Rückätzung vor stromlosem Kupfer

F4: Wie sollten Lötmaskenöffnungen für BGA-Bereiche gestaltet werden?

Design-Spezifikationen:

- Standard-BGA:

- Lötmaskenöffnungen 0,05 mm größer als Pads pro Seite

- Minimale Lötmaskenbrücke 0,1mm

- NSMD-Design (Non-Solder Mask Defined)

- Fine-Pitch BGA (≤0,5mm Abstand):

- Lötmaskenöffnungen gleich oder etwas kleiner (0,02-0,03 mm) als Pads

- SMD-Bauweise (Solder Mask Defined)

- Betrachten Sie das LDI-Verfahren (Laser Direct Imaging)

- Besondere Behandlungen:

- Verhindert das Aufsteigen der Lötmaske auf BGA-Kugeln

- Kontrolle der Dicke der Lötmaske auf 10-15μm

- Erforderlichenfalls Lötstopplacke einsetzen

Gemeinsame Problemlösung:

- Eine dicke Lötmaske verursacht Probleme beim Löten: Verwenden Sie dünne Lötmaskentinten

- Abgebrochene Lötmaskenbrücken:Optimieren Sie Belichtungsenergie und Entwicklung

- Falsch ausgerichtete Öffnungen:Fototool oder LDI-Daten überprüfen

F5: Warum kommt es bei der ENIG-Beschichtung manchmal zur Bildung von "Black Pad"? Wie kann man es verhindern?

Schwarzes Pad Ursachen:

Black Pad bezieht sich auf spröde Grenzflächen zwischen Nickel und Lot in ENIG-Oberflächen, hauptsächlich verursacht durch:

- Überätzung von Nickel bei der Goldabscheidung

- Abnormaler Nickel-Phosphor-Gehalt (sollte 7-9% betragen)

- Zu dicke Goldschicht (>0,15μm) verursacht Nickelpassivierung

- Unsachgemäße Nachbehandlung (unzureichende Reinigung)

Methoden der Prävention:

- Prozesskontrolle:

- Bad pH 4,5-5,5 beibehalten

- Kontrollgolddicke 0,05-0,10μm

- Nachbehandlung hinzufügen (z. B. Waschen mit milder Säure)

- Überwachung der Qualität:

- Regelmäßige Prüfung des Nickel-Phosphorgehalts

- Querschnittsanalyse der Nickel-Gold-Grenzfläche

- Scherprüfung von Lötkugeln (>5kg/mm²)

- Alternative Lösungen:

- Erwägen Sie ENEPIG (Chemisch Nickel Chemisch Palladium Chemisch Gold)

- Verwendung von elektrolytischem Nickel/Gold für hochzuverlässige Anwendungen

F6: Wie lassen sich Probleme der Signalintegrität bei Hochgeschwindigkeitsleiterplatten lösen?

Ko-Optimierung von Konstruktion und Fertigung:

- Auswahl des Materials:

- Materialien mit niedriger Dk (Dielektrizitätskonstante) und niedrigem Df (Dissipationsfaktor)

- Glatte Kupferfolien (z. B. HVLP)

- Design-Optimierung:

- Enge Impedanzkontrolle (±10%)

- Minimieren über Stubs (Rückwärtsbohren)

- Verwendung von Microstrip- oder Stripline-Strukturen

- Fertigungskontrollen:

- Ätzgenauigkeit (±15μm Leiterbahnbreite)

- Kontrolle der dielektrischen Dicke (±10%)

- Auswahl der Oberflächenbeschaffenheit (bevorzugt Imm Ag oder OSP)

- Prüfung der Verifizierung:

- TDR-Prüfung (Time Domain Reflectometry)

- Messungen der Einfüge-/Rückflussdämpfung

- Augendiagrammprüfung (für Hochgeschwindigkeitssignale)

Typische Parameter:

- 10 Gbps-Signale: Materialien mit Df<0,010

- 28Gbps+:Erwägen Sie Megtron6 oder Rogers-Materialien

- Impedanz:50Ω unsymmetrisch, 100Ω differenziell (Einstellung per Protokoll)

Schlussfolgerung

Die Leiterplattenherstellung ist eine multidisziplinäre Technologie, die Materialwissenschaft, chemische Prozesse und Präzisionsmechanik miteinander verbindet.Da sich die Elektronik in Richtung höherer Frequenzen, Geschwindigkeiten und Dichten entwickelt, entwickeln sich auch die Verfahren zur Herstellung von Leiterplatten entsprechend weiter. Das Verständnis dieser Fertigungsabläufe erleichtert nicht nur die Entwicklung besser herstellbarer Leiterplatten, sondern ermöglicht auch eine schnelle Fehlerbehebung und eine effektive Kommunikation mit den Herstellern.

Ganz gleich, ob Sie mit herkömmlichen FR-4-Materialien für die Unterhaltungselektronik, speziellen Hochfrequenzmaterialien für 5G-Geräte oder hochzuverlässiger Automobilelektronik arbeiten, die Auswahl geeigneter Leiterplattenhersteller und das gründliche Verständnis ihrer Fähigkeiten erweisen sich als entscheidend.Wir hoffen, dass dieser Leitfaden wertvolle Einblicke bietet, um Ihre Entscheidungsfindung in der Leiterplattenherstellung zu unterstützen.

Verwandte Beiträge