Hochgeschwindigkeits-PCB-Layoutentwurf

Inhaltsübersicht

Die Rolle von High-Speed PCB Routing Design

Eine ordnungsgemäße Verlegung gewährleistet die Signalintegrität, verbessert die elektromagnetische Verträglichkeit (EMV) und erhöht die Zuverlässigkeit des Systems.

1. Sicherstellung der Signalintegrität

Eine gut durchdachte Routing-Strategie kann die Signalreflexion und das Übersprechen minimieren und so die stabile Übertragung von Hochgeschwindigkeitsdaten (wie USB 3.0, HDMI usw.) auf der Leiterplatte gewährleisten.

2. Elektromagnetische Verträglichkeit

Durch die Einführung eines vernünftigen Rastersystems zur Standardisierung der Routing-Kanäle können Konflikte bei den Bauteilabständen reduziert werden; differentielle Signalisierung, Abschirmungsschichten und Erdungsebenen für die Stromversorgung können elektromagnetische Störungen (EMI) minimieren.

3. Systemzuverlässigkeit

Durch die Kontrolle der Routingdichte und der Ressourcennutzung können redundante Pfade minimiert und die Kosten gesenkt werden; Blind Vias und Buried Vias können das Routing bei hoher Dichte optimieren. Standardisierte Rasterlayouts können Kurzschlussrisiken verhindern.

Grundlagen des Hochgeschwindigkeits-PCB-Designs

1. Schlüsselelemente der Signalintegrität (SI)

- Auswirkungen von Übertragungsleitungen: Hochfrequenzsignale erfordern die Berücksichtigung der Übertragungsleitungstheorie zur Kontrolle der Anpassung der charakteristischen Impedanz

- Unterdrückung der Reflexion: Verwenden Sie Abschlusswiderstände, um Signalreflexionen zu reduzieren.

- Nebensprechkontrolle: Anwendung der 3W-Regel zur Minimierung des Nahnebensprechens (NEXT) und des Fernnebensprechens (FEXT)

2. Grundlagen der Energieintegrität (PI)

- Stromverteilungsnetz (PDN): Optimieren Sie das Design der Leistungs-Masse-Ebene

- Entkopplungskondensatoren: Implementierung von Entkopplungsnetzwerken mit "10μF+0,1μF+0,01μF"-Kombinationen

- Gleichzeitiges Schaltrauschen (SSN): Reduzieren Sie die Auswirkungen gleichzeitiger Schaltausgänge (SSO) durch eine geeignete Anordnung

Hochgeschwindigkeit PCB Stackup Design

1. Mehrschichtige Platinenstapelstruktur

- Typische Stapelung: Empfohlene 8-Schicht-Konfiguration (oben-Gnd-Sig-Pwr-Sig-Gnd-Sig-unten)

- Impedanzkontrolle: Erzielen Sie 50Ω Single-Ended- und 100Ω Differenzimpedanz durch Stackup-Design

- Dielektrische Materialien: Auswahl von Hochfrequenz-Plattenmaterialien mit niedriger Dielektrizitätskonstante (Dk) und niedrigem Verlustfaktor (Df)

2. Erweiterte Anwendung der 20H-Regel

- Vertiefung der Leistungsebene: Die Stromversorgungsebene sollte 20H gegenüber der Grundplatte einrücken.

- EMI-Unterdrückung: Reduziert effektiv die Kantenstrahlung um 30-40 dB

- Mobile Geräte: Schutzringe und Durchkontaktierungen hinzufügen

Hochgeschwindigkeits-Signal-Routing-Techniken

1. Differentialsignalisierung - Routing

- Anpassung der Länge: Kontrolle der Längenanpassung von Differentialpaaren innerhalb von ±5mil

- Phasenanpassung: Beibehaltung der Phasendifferenz zwischen positiven/negativen Signalen <5ps

- Intra-Pair-Verzögerung: Strenge Kontrolle des Intra-Paar-Versatzes

2. Besondere Behandlung von Taktsignalen

- Spuren bewachen: Platzieren Sie Schutzleiterbahnen auf beiden Seiten der Taktlinien

- Terminierungsverfahren: Quellterminierung oder Endterminierung verwenden

- Jitter-Kontrolle: Reduzierung des Timing-Jitters durch Low-Jitter-Taktverteilungsnetzwerke

Optimierung der Leistungsintegrität

1. Entwurf eines Stromverteilungsnetzes (PDN)

- Ziel-Impedanz: Halten Sie die PDN-Impedanz über alle Frequenzen hinweg unter dem Zielwert

- Kapazität der Ebene: Nutzung der Eigenkapazität zwischen Stromversorgungs- und Erdungsebene

- Frequenzabdeckung: Das Entkopplungsnetzwerk sollte den DC- bis GHz-Bereich abdecken

2. Unterdrückung von gleichzeitigem Schaltrauschen (SSN)

- Segmentierung der Leistung: Verschiedene Spannungsbereiche richtig segmentieren

- Rückweg: Sicherstellen, dass Hochgeschwindigkeitssignale einen niederohmigen Rückkanal haben

- Über die Vermittlung: Ausreichende Leistungsdurchführungen zur Verringerung der Schleifeninduktivität

EMC/EMI-Entwurf

1. Elektromagnetische Verträglichkeit (EMC) Design

- Kontrolle der Strahlung: Verringerung der Strahlungsemissionen durch die 20H-Regel und Schutzstreifen

- Empfindliche Schaltkreise: Abschirmung für RF-empfindliche Schaltungen implementieren

- Entwurf des Filters: Installieren Sie π-Filter oder T-Filter an den E/A-Schnittstellen

2. Optimierung des Bodensystems

- Hybride Erdung: Implementierung einer hybriden Erdungsstrategie für digitale/analoge Schaltungen

- Steuerung der Segmentierung: Vermeidung von Ground Bounce durch unsachgemäße Segmentierung der Grundplatte

- Mehrpunkt-Erdung: Verwenden Sie für Hochfrequenzstromkreise eine Mehrpunkterdung

Hochgeschwindigkeits-PCB-Design-Verifizierung

1. Analyse der Signalintegrität (SI)

- Analyse im Zeitbereich: Bewertung der Signalqualität durch Augendiagramme

- Analyse im Frequenzbereich: Analysieren der Übertragungseigenschaften mit S-Parametern

- Überprüfung der Simulation: Durchführung von Pre-Layout- und Post-Layout-Simulationen mit HyperLynx oder ADS

2. Überprüfung der Leistungsintegrität (PI)

- Impedanzprüfung: Durchführung von PDN-Impedanztests vom VRM zum Chip

- Rauschmessung: Messung von Leistungswelligkeit und Rauschen

- Thermische Analyse: Bewertung des Temperaturanstiegs von Hochstrom-Leiterbahnen

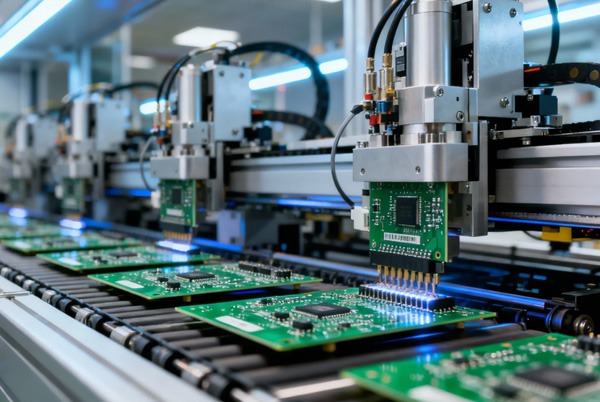

Herstellungsprozess

1. Entwurf für die Fertigung (DFM)

- Kontrolle der Leiterbahnbreite: Auswirkungen des Ätzfaktors berücksichtigen

- Seitenverhältnis: Halten Sie das Verhältnis von Plattendicke zu Lochdurchmesser <8:1

- Oberflächengüte: Bevorzugt ENIG- oder Chemisch Silber-Oberflächenbehandlungen

2. Auswahl des Materials

Durch die Anwendung dieser Prinzipien für das Layout von Hochgeschwindigkeits-Leiterplatten und die Optimierung von Schlüsselwörtern können die Signalintegrität, die Leistungsintegrität und die EMV-Leistung von Hochgeschwindigkeits-Leiterplatten erheblich verbessert werden. Während des Entwurfsprozesses sollte besonderes Augenmerk auf Schlüsselfaktoren wie Impedanzkontrolle, Reduzierung des Übersprechens und Optimierung der Leistungsintegrität gelegt werden, wobei auch Simulations- und Messmethoden zur Überprüfung eingesetzt werden sollten.

Wichtige Überlegungen für das High-Speed PCB Routing Design

Impedanzkontrolle und Auswahl der Übertragungsleitung

Die Impedanzkontrolle ist entscheidend für Hochgeschwindigkeits-Leiterplatte Entwurf. Wählen Sie die geeignete Übertragungsleitungsstruktur (z.B. Microstrip oder Stripline) basierend auf der Signalfrequenz, der Leiterplattendicke und der Dielektrizitätskonstante. Verwenden Sie Tools zur Impedanzberechnung (z. B. Polar SI9000 oder den integrierten Rechner von Altium Designer), um die Impedanz der Leiterbahn genau zu bestimmen und sicherzustellen, dass sie den Designanforderungen entspricht. Beispielsweise erfordern differentielle Paare in der Regel eine Impedanz von 90Ω oder 100Ω, was eine strenge Kontrolle der Leiterbahnbreite und -abstände erforderlich macht. Vermeiden Sie Impedanzdiskontinuitäten, die durch rechtwinklige Biegungen, Durchkontaktierungen, Verzweigungen oder plötzliche Änderungen der Leiterbahnbreite verursacht werden, da diese zu Signalreflexionen und verminderter Integrität führen können.

Routing-Strategien zur Reduzierung des Übersprechens

Übersprechen ist eine große Gefahr für die Integrität von Hochgeschwindigkeitssignalen. Um seine Auswirkungen zu minimieren:

- Abstand der Leiterbahnen vergrößern: Befolgen Sie die 3W-Regel (Abstand zwischen benachbarten Leiterbahnen ≥ 3× Leiterbahnbreite), um die elektromagnetische Kopplung zu reduzieren.

- Differentialsignalisierung verwenden: Differentialpaare (z. B. USB, PCIe, LVDS) unterdrücken effektiv Gleichtaktstörungen, erfordern jedoch eine präzise Impedanzanpassung der Leiterbahnbreite und -abstände sowie eine strikte Längenanpassung.

- Abschirmschichten hinzufügen: Verlegen Sie Masseflächen (GND) um empfindliche Signale (z. B. Taktleitungen, HF-Signale), um externe Störungen zu isolieren.

- Vermeiden Sie lange parallele Leiterbahnen: Parallele Streckenführung erhöht die Kopplung - wählen Sie stattdessen orthogonale Kreuzungen oder größere Abstände.

Minderung von Reflexionen und Optimierung der Signalintegrität

Signalreflexionen können Überschwingen, Klingeln und andere Stabilitätsprobleme verursachen. Zu den Optimierungsmethoden gehören:

- Kontrolle der Leiterbahnlänge: Hochgeschwindigkeitssignale (z. B. DDR, HDMI) erfordern eine strikte Längenanpassung, um Zeitverzögerungen aufgrund von Ausbreitungsverzögerungen zu vermeiden.

- Impedanzanpassung mit Abschlusswiderständen: Wählen Sie die geeignete Abschlussmethode (Serien-, Parallel- oder Thevenin-Terminierung) auf der Grundlage der Eigenschaften der Übertragungsleitung, um Reflexionen zu vermeiden.

- Optimierung von Leistungs- und Bodenebenen: Verwenden Sie niederohmige Leistungsschichten und solide Masseflächen zusammen mit strategisch platzierten Entkopplungskondensatoren (z. B. Kombinationen aus 0,1μF und 10μF), um das Leistungsrauschen zu verringern.

Endgültiger Entwurf und Verifizierung

Führen Sie nach Abschluss der Entflechtung einen Design Rule Check (DRC) durch, um die Einhaltung der PCB-Herstellungsanforderungen sicherzustellen. Verwenden Sie SI/PI (Signal Integrity/Power Integrity)-Simulationswerkzeuge (z. B. HyperLynx oder ADS), um kritische Signalpfade zu validieren und potenzielle Probleme frühzeitig zu erkennen.

Durch die Umsetzung dieser Maßnahmen kann die Signalqualität in Hochgeschwindigkeits-Leiterplatten erheblich verbessert werden, wodurch die Stabilität und Zuverlässigkeit des Systems gewährleistet wird.

Verwandte Empfehlungen

Leitfaden für Design und Layout von Hochfrequenz-Leiterplatten

Verwandte Beiträge