Piirilevyjen valmistusvirheet ovat harvoin satunnaisia.

Useimmat viat ovat peräisin suunnittelupäätökset, materiaalin rajoitukset tai prosessin epävakaus.kauan ennen lopputarkastusta.

Vaikka tarkastuksella voidaan havaita monia näkyviä ongelmia, vikojen ennaltaehkäisyn on tapahduttava valmistusprosessin varhaisemmassa vaiheessa.

Tässä artikkelissa selitetään yleisimmät piirilevyjen valmistusvirheet, niiden perimmäiset syyt ja käytännön ennaltaehkäisystrategiat valmistuksen näkökulmasta.

Laadun perusteet, ks: Mikä määrittää PCB-laadun?

Sisällysluettelo

Mitä pidetään PCB-valmistusvirheenä?

PCB-valmistusvirhe on mikä tahansa poikkeama, joka:

- Vaikuttaa sähköiseen suorituskykyyn

- Vaarantaa mekaanisen eheyden

- Vähentää pitkän aikavälin luotettavuutta

- Rikkoo IPC:n tai asiakkaan eritelmiä

Viat voivat olla näkyvä, latentti, tai progressiivinen, jotka ilmenevät vasta lämpö- tai mekaanisen rasituksen jälkeen.

Sisäisen kerroksen viat

Yleiset sisäisen kerroksen viat

- Avoimet piirit

- Oikosulut

- Yli- tai alietsaus

- Kerrosten välinen virheellinen rekisteröinti

Juurisyyt

- Kuvantamisen epätarkkuudet

- Syövytysprosessin vaihtelu

- Huono sisäkerroksen kohdistus

Koska sisäkerrokset suljetaan laminoinnin aikana, tässä vaiheessa syntyvät viat ovat peruuttamaton.

Prosessin tausta: Sisäkerroksen valmistuksen selitys

Poraukseen liittyvät viat

Tyypilliset porausvirheet

- Epäkeskeiset reiät

- Purseet ja tahra

- Rikkinäiset poranterät

- Reiän seinämän huono laatu

Juurisyyt

- Liian suuri poraussuhde

- Kuluneet työkalut

- Väärä syöttö ja nopeus

- Epäasianmukainen porausmenetelmä

Porausvirheet vaikuttavat suoraan kuparipinnoituksen laatuun ja luotettavuuteen.

Menetelmien vertailu:

PCB-poraus vs. laserporaus

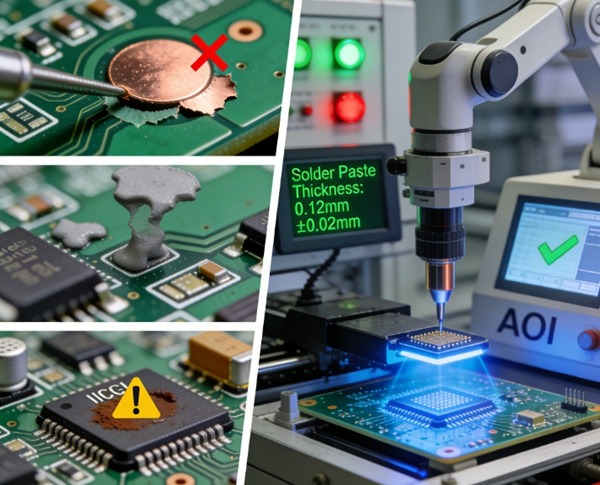

Pinnoitusvirheet

Yleiset pinnoitusongelmat

- Ohut kupari läpivienneissä

- Tyhjät tilat tai aukot

- Karkea tai nodulaarinen kupari

- Huono tarttuvuus

Juurisyyt

- Virheellinen pinnan valmistelu

- Epäjohdonmukainen virrantiheys

- Kemiallinen epätasapaino

- Suuren kuvasuhteen läpiviennit

Pinnoitusvirheet ovat merkittävä syy ajoittaiset viat ja lämpökierron aiheuttamat ongelmat.

Prosessin yksityiskohdat: Kuparointiprosessi PCB-valmistuksessa

Syövytysviat

Tyypilliset syövytysvirheet

- Yli syövytetyt jäljet

- Kuparisillat, jotka ovat alta syövytettyjä

- Viivan leveyden vaihtelu

- Trace kaulan alaspäin

Juurisyyt

- Epätasainen kuparin paksuus

- Aggressiivinen etsauskemia

- Huono prosessikorvaus

- Tiukka jäljen väli

Kun jäljen geometria muuttuu yhä hienommaksi, etsausvirheet vaikuttavat yhä enemmän tuottoon ja luotettavuuteen.

Tuottokeskeinen analyysi: PCB Etching prosessi ja tuoton valvonta

Laminointi- ja delaminointiviat

Yleiset laminointiongelmat

- Delaminaatio

- Blistering

- Hartsin tyhjät tilat

- Kerrossiirtymä

Juurisyyt

- Väärä laminointipaine tai -lämpötila

- Huono prepreg-valinta

- Kosteuden imeytyminen

- Epätasapainoiset pinot

Nämä viat ilmenevät usein kokoonpanon tai lämpökierron aikana eikä niinkään alkuperäisen testauksen aikana.

Aineellinen suhde: PCB-materiaalin ja kerroksen kustannukset

Juotosmaski- ja pintakäsittelyvirheet

Tyypilliset viat

- Juotosmaskin väärä suuntaus

- Huono tarttuvuus

- Neulanreiät

- Epätasainen pintakäsittelyn paksuus

Juurisyyt

- Riittämätön pinnan valmistelu

- Väärät kovettumisolosuhteet

- Prosessin saastuminen

Nämä viat voivat johtaa juotossiltojen muodostumiseen, korroosioon ja lyhentyneeseen säilyvyysaikaan.

Sähkötestauksen karkaamiset ja piilevät viat

Kaikkia vikoja ei havaita sähkötestauksessa.

Piilevät viat voivat:

- Läpäisee alustavat testit

- Epäonnistuu lämpörasituksen jälkeen

- Ilmestyvät kenttätoiminnan aikana

Yleisiä syitä ovat:

- Reunapinnoituksen paksuus

- Läpivientien mikrohalkeamat

- CAF:n muodostaminen

Suunnitteluun liittyvät puuteriskit

Jotkin viat johtuvat pikemminkin suunnitteluvalinnoista kuin valmistusvirheistä.

Korkean riskin suunnittelutekijöitä ovat muun muassa:

- Erittäin hienot jäljet ja välit

- Suuren kuvasuhteen läpiviennit

- Epätasapainoinen kuparijakelu

- Liian tiukat toleranssit

Laadukas liitäntä: PCB-suunnittelun kustannustekijät

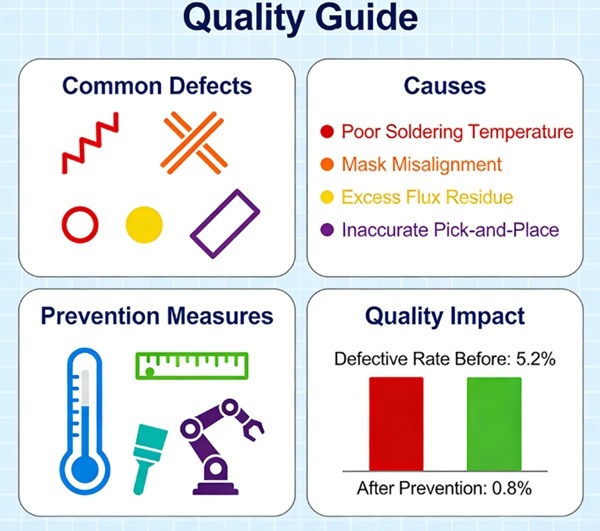

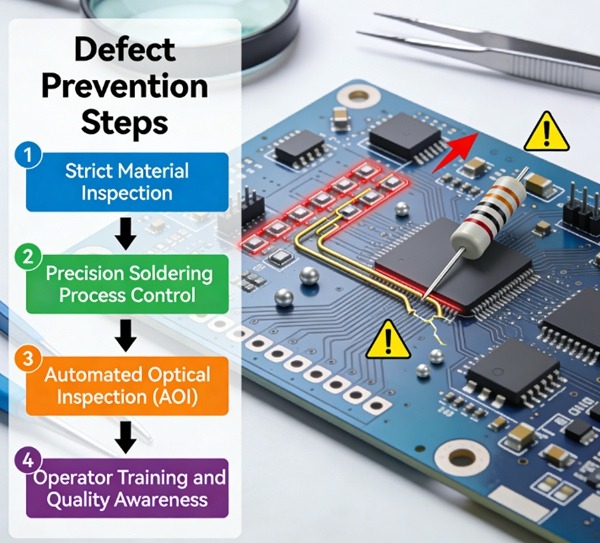

Kuinka estää PCB-valmistusvirheet

Tehokkaassa vikojen ehkäisyssä keskitytään prosessin vakaus, ei vain tarkastusta.

Tärkeimpiä ennaltaehkäisystrategioita ovat:

- Varhainen DFM-arviointi

- Konservatiiviset suunnittelumarginaalit

- Pätevän materiaalin valinta

- Prosessin kyvykkyyden seuranta

- Tuottotietojen analysointi

TOPFASTissa vikojen ennaltaehkäisyä ohjaavat seuraavat tekijät tuotantoketjun alkupään prosessinohjaus ja tietoon perustuva palaute, mikä vähentää riippuvuutta loppuvaiheen seulonnasta.

Virheiden ehkäisy vs. valmistuskustannukset

Vikojen ehkäiseminen vähentää usein kokonaiskustannuksia.

Etuihin kuuluvat:

- Suurempi tuotto

- Vähemmän jälkitöitä

- Vähemmän viivästyksiä

- Pienempi kenttävikojen riski

Kustannusten ja laadun tasapaino: PCB:n valmistuskustannukset selitetty

Päätelmä

Piirilevyjen valmistusvirheet ovat harvoin yksittäisiä tapauksia.

Ne ovat seurausta suunnittelun, materiaalien ja prosessinvalvonnan välinen vuorovaikutus.

Kun insinöörit ja ostajat ymmärtävät yleiset vikatyypit ja niiden perimmäiset syyt, he voivat ryhtyä ennakoiviin toimiin vikojen ehkäisemiseksi ja pitkän aikavälin luotettavuuden parantamiseksi.

Tämä artikkeli on keskeinen pilari PCB laatu ja luotettavuus klusteri.

FAQ: PCB Manufacturing Defects

V: Syövytykseen liittyvät viat ja pinnoitusongelmat ovat yleisimpiä.

V: Ei. Tarkastus havaitsee viat, mutta ei ehkäise niiden perimmäisiä syitä.

V: Kokoonpanon aikana syntyvä lämpöjännitys voi paljastaa aiemmin syntyneet piilevät viat.

V: Ei. Monet viat johtuvat suunnittelusta tai materiaalivalinnoista.

V: DFM-tarkastelun ja konservatiivisen suunnittelun avulla, joka on linjassa prosessikyvyn kanssa.