Como conceber o controlo de impedância para PCB?

Índice

A importância do controlo da impedância da placa de circuito impresso

Nos actuais dispositivos electrónicos de alta velocidade, as velocidades de transmissão do sinal são cada vez mais rápidas e o controlo da impedância da placa de circuito impresso tornou-se um fator essencial para determinar o êxito ou o fracasso de um projeto. O desfasamento da impedância pode causar problemas de reflexão do sinal, de toque e de ultrapassagem, que afectam seriamente a integridade do sinal. De acordo com as estatísticas, mais de 60% das falhas dos circuitos digitais de alta velocidade estão relacionadas com um controlo inadequado da impedância. Por conseguinte, é essencial dominar a tecnologia de controlo da impedância da placa de circuito impresso.

Os quatro pilares do controlo de impedância

1. Seleção de materiais

"Escolha o material certo e estará a meio caminho do sucesso";-Isto é especialmente verdadeiro no controlo da impedância:

- Materiais de alta frequência recomendados: Rogers RO4350B (εr=3,48), Isola I-Tera MT40 (εr=3,45) e outros materiais de baixa perda são escolhas ideais.

- Limitações do FR4 tradicional: As grandes flutuações da constante dieléctrica (4,2-4,7) e a elevada tangente de perda (0,02) tornam-no inadequado para aplicações acima de 10GHz.

- Seleção de folha de cobre: A folha de cobre de baixo perfil (folha LP) reduz a rugosidade da superfície em 30% em comparação com a folha normal, diminuindo significativamente as perdas de alta frequência.

Dica de especialista: Para frequências de ondas milimétricas (24 GHz e superiores), considere materiais de perda ultra-baixa como o Rogers RT/duroid 5880 (εr=2,2).

2.Conceção laminada

Um excelente projeto de empilhamento deve ter em conta:

- Estrutura simétrica: Evita a deformação da placa, tal como uma disposição simétrica "sinal-terra-sinal".

- Espessura da camada intermédia: Valores típicos recomendados:

- Camada de superfície de extremidade única de 50Ω:Espessura dieléctrica de 5-6mil (largura do traço 8-10mil).

- Camada interior de extremidade única de 50Ω:Espessura dieléctrica de 4-5mil (largura do traço 5-7mil).

- Planos de referência: Assegurar que as camadas de sinal são adjacentes a planos de terra completos, evitando divisões.

Estudo de casoUma placa de 6 camadas optimizada para empilhamento melhorou a integridade do sinal em 40%:

Camada1:Sinal (microstrip)

Layer2: Plano de terra sólido

Layer3: Sinal (stripline)

Camada4: Sinal (stripline)

Camada5: Plano de terra sólido

Camada6: Sinal (microstrip) Consultar um profissional de conceção de PCBum design científico de empilhamento de camadas garante a fiabilidade da placa de circuito impresso

3.Conceção da cablagem

Fórmula de impedância (aproximação microstrip):

Z₀ ≈ (87/√(εr+1.41)) × ln(5.98h/(0.8w+t))

Onde:

- Z₀: Impedância caraterística (Ω)

- εr:Constante dieléctrica relativa

- h:Espessura dieléctrica (mil)

- w:Largura do traço (mil)

- t:Espessura do cobre (mil)

Conselhos práticos:

- Utilize as calculadoras de impedância Polar Si9000 ou Altium para efetuar cálculos precisos.

- Siga a regra "3W" para pares diferenciais: Espaçamento ≥ 3× largura do traço.

- Corresponder comprimentos de sinais críticos com uma tolerância de ±5mil.

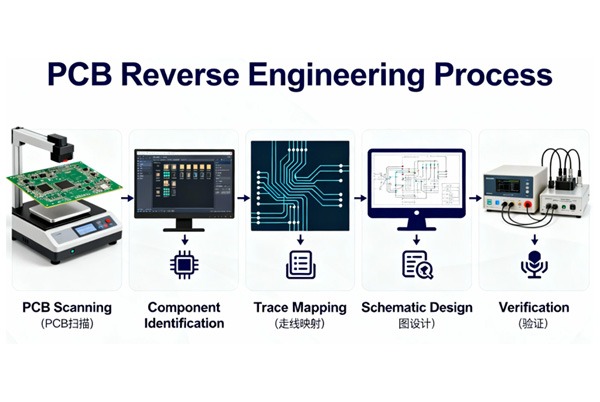

4.Processo de fabrico

Ao colaborar com Fabricantes de PCB, confirmar:

- Tolerância de impedância: Tipicamente ±10%, ±7% para aplicações topo de gama.

- Espessura do cobre acabado: 1oz de cobre ≈ 1,4mil (35μm) de espessura efectiva.

- Variação da espessura dieléctrica: Normalmente dentro de ±10%.

- Acabamento da superfícieO ENIG é melhor do que o HASL para aplicações de alta frequência.

Problemas comuns de controlo de impedância & Soluções

Questão 1: Descontinuidade de impedância induzida por via

Soluções:

- Utilizar a perfuração de retorno para remover o excesso de via stubs.

- Adicionar vias de terra perto de vias de sinal crítico (espaçamento <150mil).

- Utilizar microvias (<6mil) para reduzir os efeitos parasitas.

Problema 2: Incompatibilidade de impedância da zona de transição do conetor

Soluções:

- Conceber traços cónicos para transições de impedância suaves.

- Utilizar estruturas de guia de ondas coplanares para melhorar a continuidade de terra.

- Selecione conectores com impedância correspondente (por exemplo, série Samtec SEARAY).

Problema 3: Radiação da borda da placa causando flutuação de impedância

Soluções:

- Implementar a "regra 20H": Plano de potência inserido por 20× a espessura do dielétrico.

- Adicionar terra através de matrizes ao longo das extremidades (espaçamento <λ/10).

- Aplicar estruturas de banda electromagnética (EBG) para suprimir a radiação de borda.

Estudo de caso: Otimização da impedância do canal SerDes de 10Gbps

Desafio: Um PCB de switch empresarial apresentou erros de dados intermitentes.

Análise:

- O teste TDR revelou uma variação de impedância de 15%.

- Causa principal: Vias de terra insuficientes à volta dos pares diferenciais.

- Os traços de superfície não tinham em conta os efeitos da máscara de soldadura.

Solução:

- Aumento da densidade de via terrestre (uma por 200mil).

- Largura de traço ajustada para compensação da máscara de soldadura (5mil→4,8mil).

- Comutado para máscara de solda de baixo Dk (εr=3,0).

Resultado: Variação de impedância reduzida para <5%, taxa de erro de bit melhorada 100×!

Conceção profissional de controlo da impedância consultoria para salvaguardar a sua conceção eletrónica.

Tecnologias emergentes

- Materiais com perdas ultra-baixas: por exemplo, Panasonic MEGTRON6 (Df=0,002).

- Tecnologia dieléctrica híbrida: Combinação de materiais com diferentes valores de Dk para otimização da impedância localizada.

- PCBs impressos em 3D: Possibilitar estruturas de impedância graduada.

- Conceção assistida por IAAutomatização da otimização da rede de casamento de impedâncias.

Lista de controlo do engenheiro

Antes de enviar para o fabrico de PCB, verificar:

Confirmação das especificações do material e das capacidades do processo com o fabricante.

Realização de simulação de impedância para redes críticas.

Cumpriu os requisitos de correspondência do comprimento do par diferencial.

Optimizado através de estruturas.

Concebeu cupões de teste.

Especificações de impedância documentadas.

Com o rápido desenvolvimento das tecnologias 5G, IA e IoT, a demanda por integridade de sinal de alta velocidade só continuará a crescer. Ao dominar a tecnologia central do controle de impedância de PCB, você será capaz de se destacar no design de PCB de alta velocidade e garantir a estabilidade e confiabilidade de seus produtos.

Publicações relacionadas