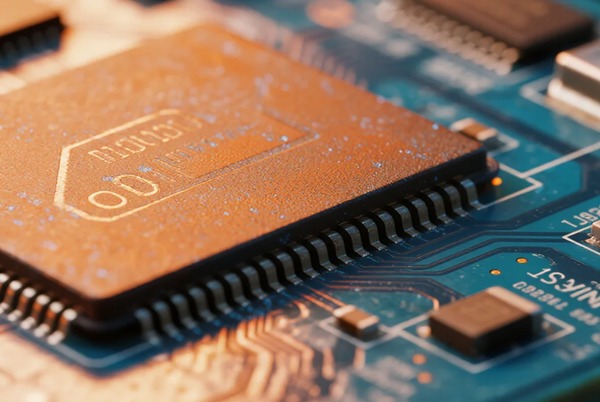

Como melhorar o desempenho e a confiabilidade da placa de circuito impresso?

Utilizando uma abordagem sistemática para otimizar o PCB o processo de conceção pode melhorar eficazmente o desempenho e a fiabilidade dos Conceção de PCB e assegurar o funcionamento estável dos dispositivos electrónicos.

Índice

Estratégias de conceção essenciais e práticas inovadoras

1. Disposição de precisão e encaminhamento inteligente

- Implementar a divisão modular em zonas com isolamento analógico/digital de ≥5 mm

- Aplicar a regra 3W para componentes de alta velocidade (espaçamento≥3×largura do traço)

- Colocação de tabuleiro de xadrez com consciência térmica com matrizes de vias de arrefecimento de 0,5 mm

2. Rede avançada de fornecimento de energia

- Redes de filtros π (configuração 100μF+0,1μF+10nF)

- Simulação de integridade de potência (impedância alvo<50mΩ@1MHz)

- Tecnologia de capacitância incorporada (densidade de 50nF/cm²)

3. Soluções de integridade de sinal de alta velocidade

- Controlo do par diferencial: ±2,5mil de correspondência de comprimento

- Controlo da impedância: tolerância de ±10% (verificado por HSPICE)

- Tecnologia de perfuração posterior (comprimento do tubo <12mil)

4. Gestão térmica 4.0

- Simulação térmica 3D (ΔT<15℃ alvo)

- Sistemas de arrefecimento híbridos:

- Cobre de 2oz + vias térmicas (φ0.3mm@1mm passo)

- Fixação selectiva do dissipador de calor (>5W/mK)

5. Matriz de defesa EMI/EMC

- Proteção de gaiola de Faraday (>60dB@1GHz)

- Conjuntos de esferas de ferrite (100Ω@100MHz)

- Planos de terra segmentados (cruzamentos<λ/20)

Inovações na produção

6. Normas DFM 2.0

- Controlos de processos HDI:

- Microvias laser: φ75±15μm

- Alinhamento das camadas: ±25μm

- Prototipagem impressa em 3D (prazo de entrega de 24 horas)

7. Ecossistema de testes inteligentes

- Varrimento de limites JTAG (cobertura >95%)

- Sistemas de teste baseados em IA:

- TDR automatizado (resolução de ±1%)

- Imagem térmica em tempo real (resolução de 0,1℃)

Melhorias de fiabilidade

8. Robustez de nível militar

- Ensaio HALT (conformidade 6σ)

- Tecnologia de nanorrevestimento (300% proteção melhorada)

- Circuitos de auto-cura (MTBF>100.000hrs)

9. Arquitetura de empilhamento da próxima geração

- Empilhamento de materiais híbridos:

- Camadas RF: Rogers 4350B (εr=3,48)

- Camadas padrão: FR-4 de alta Tg (>170℃)

- Tecnologia de componentes incorporados (aumento da integração 40%)

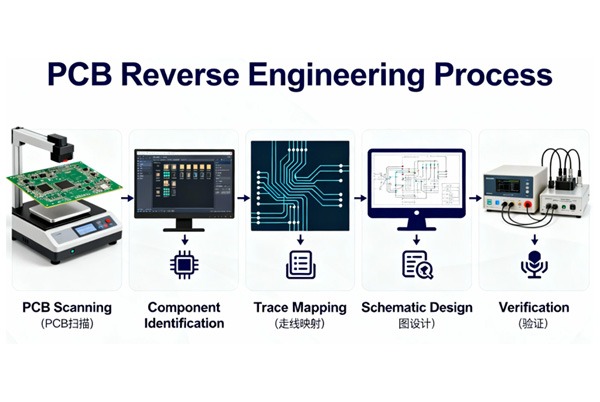

Metodologia de verificação

10. Validação do ciclo de vida completo

- Verificação por fases:

- Simulação SI/PI pré-layout

- Protótipo de ensaio TDR

- Validação HASS de produção

- Modelação de gémeos digitais (precisão de previsão >90%)

Avaliação comparativa do desempenho

| Parâmetro de projeto | Convencional | Optimizado | Melhoria |

|---|---|---|---|

| Perda de sinal | 6dB@10GHz | 3dB@10GHz | 50% |

| Ruído de potência | 50mVpp | 15mVpp | 70% |

| Resistência térmica | 35℃/W | 18℃/W | 48% |

| Margem EMC | 3dB | 10dB | 233% |

Casos de implementação no sector

Avanços na estação de base 5G:

- Transmissão mmWave a 77GHz

- <8mVrms de ruído de potência

- <8℃/cm² de gradiente térmico

Sistemas de energia EV:

- Barramentos empilhados de 200A

- 150℃ funcionamento contínuo

- Certificação ISO 26262 ASIL-D

Publicações relacionadas