Vanliga problem vid förbättring av kretskortens tillförlitlighet

Innehållsförteckning

Hur beräknar man PCB-impedans?

Beräkning av PCB-impedans säkerställer signalintegritet, särskilt för höghastighets- och RF-kretsar.

1. Bestäm PCB-stackup och -geometri

- Antal lager: Enkelt, dubbelt eller flerskiktat.

- Spårets bredd (W) och tjocklek (T): Avgörande för impedansreglering.

- Dielektrisk tjocklek (H): Avstånd mellan signalskikt och referensplan (t.ex. mark).

- Vikt koppar: Vanligtvis 0,5 oz (17,5 µm) till 2 oz (70 µm).

2. Identifiera dielektricitetskonstant (Dk eller εᵣ)

- FR-4: ~4,3-4,8 (varierar med frekvensen).

- Rogers RO4003C: ~3,38 (låg förlust för RF).

- Polyimid: ~3,5 (flexibla kretskort).

- Notera: Dk minskar något vid högre frekvenser.

3. Välj metod för impedansberäkning

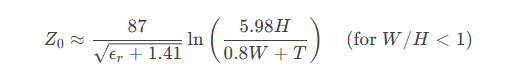

Mikrostrip (yttre lager spår över jordplan):

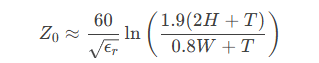

Stripline (inre skikt mellan två jordplan):

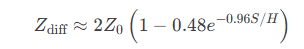

Differentiellt par: Kräver avstånd (S) mellan spåren.

4. Använd impedansberäknare eller verktyg

- Verktyg online: Saturn PCB Toolkit, EEWeb Kalkylator.

- PCB-programvara: Altium Designer, KiCad eller Cadence har inbyggda impedansberäknare.

- EM-simulatorer: Ansys HFSS, CST (för avancerade konstruktioner).

5. Optimera designen baserat på resultaten

- Justera spårbredd (↑ bredd → ↓ impedans).

- Modifiera dielektrisk tjocklek (↑ H → ↑ impedans).

- Justera spåravstånd för differentiella par.

- Välj material med lämplig Dk (t.ex. Rogers för RF).

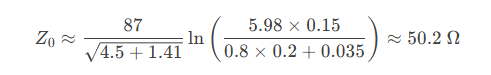

Exempel på beräkning (FR-4 Microstrip)

Givetvis:

- Spårets bredd (W) = 0,2 mm

- Dielektrisk tjocklek (H) = 0,15 mm

- Koppartjocklek (T) = 0,035 mm

- εᵣ = 4,5

Med hjälp av mikrostripformeln:

Motsvarar standard 50Ω impedans för RF-signaler.

Hur man tar hänsyn till signalintegritet i PCB-design?

1. Design av layout

Vid PCB-layoutdesign är det viktigt att ta hänsyn till layouten för signalledningar, kraftledningar och jordledningar och att undvika störningar som orsakas av korsningen av signalledningar, kraftledningar och jordledningar. Dessutom är det viktigt att minimera signallinjernas längd för att minska överhörning och fördröjning.

2. Impedansanpassning

Vid konstruktion av höghastighetssignalledningar måste impedansanpassning utföras för att säkerställa att signalledningarnas impedans matchar signalkällans och belastningens impedans och därigenom undvika signalreflektion och överhörning.

3. Dragning av signalledning

Vid mönsterkortsdesign påverkar även routningen av signalledningar signalintegriteten och måste följa vissa regler. Till exempel bör differentiella signalledningar ha ett visst avstånd och dras parallellt, medan single-ended signalledningar bör dras parallellt med jordledningar och signalledningarnas böjningar bör minimeras.

4. Strömförsörjning och jordning

Vid mönsterkortsdesign påverkar utformningen av strömförsörjning och jordning också signalintegriteten. Stabil strömförsörjning och jordning bör användas, och resistansen och induktansen i strömförsörjning och jordning bör minimeras så mycket som möjligt.

5. Verifiering av simulering

När mönsterkortsdesignen är klar krävs simuleringsverifiering för att säkerställa att signalintegriteten uppfyller kraven. Genom simulering kan problem som signalfördröjning, reflektion och överhörning upptäckas och kretskortsdesignen kan optimeras.

Hur tar man hänsyn till elektromagnetisk kompatibilitet (EMC) i PCB-design?

1. PCB-layout för EMC

- Minimera parallell routning: Undvik långa parallella dragningar mellan signal- och ström-/jordledningar för att minska överhörning och elektromagnetisk koppling.

- Isolering av kritiska signaler: Separera höghastighetssignaler (t.ex. klockor, RF) och känsliga analoga signaler från brusiga kretsar (t.ex. switchande nätaggregat).

- Strategi för stapling av lager:

- Använd solida jordplan intill signalskikten för att åstadkomma skärmning.

- Dra höghastighetssignaler på inre lager mellan jordplan för inneslutning.

2. Tekniker för jordning

- Jordplan med låg impedans: Använd obrutna jordplan för att minimera jordslingor och minska utstrålad emission.

- Dela upp marken försiktigt: Separera analog/digital jord endast när det är nödvändigt, med en enda anslutningspunkt (t.ex. ferritpärla eller 0Ω-motstånd).

- Via Stitching: Placera flera jordade vior runt högfrekventa spår eller kortkanter för att dämpa resonanser i hålrummen.

3. Filtrering och undertryckning

- Ferritpärlor: Komplettera kraft-/IO-ledningar för att blockera högfrekvent brus.

- Frikopplingskondensatorer: Placera nära IC:s strömstift (t.ex. 0,1 μF + 1 μF) för att filtrera hög- och mellanfrekvent brus.

- Common-Mode-drosslar: Används på differentiella par (t.ex. USB, Ethernet) för att undertrycka common-mode-strålning.

4. Skärmning och gränssnittsdesign

- Skärmning av kabel: Använd skärmade kontakter (t.ex. USB, HDMI) med 360° jordning till chassit.

- Skärmning på kretskortsnivå: Lägg metallburkar eller ledande beläggningar över känsliga RF-kretsar.

- Kantskydd: Dra känsliga spår bort från kortets kanter; använd skyddsspår eller jordad koppar runt dem.

5. Simulering och testning

- Analys före layouten: Använd verktyg som ANSYS HFSS eller CST för att modellera hotspots för strålning.

- Verifiering efter layouten:

- Genomför närfältsskanningar för att identifiera utsläppskällor.

- Utför överensstämmelseprovning (t.ex. FCC, CE) för utstrålade/ledda emissioner.

- Design iteration: Optimera baserat på testresultat (t.ex. genom att lägga till avslutningsmotstånd eller justera spåravståndet).

Exempel på korrigeringar:

- En klocka på 100 MHz strålar för mycket: Lägg till serieavslutningsresistorer eller dra mellan jordplan.

- Brus från växlande strömförsörjning: Implementera π-filter (LC) vid ingång/utgång.

Genom att integrera dessa metoder kan mönsterkort uppfylla EMC-standarder (t.ex. IEC 61000) samtidigt som kostsamma omkonstruktioner minimeras. Prototypa och testa alltid tidigt!

Hur tar man hänsyn till Power Integrity (PI) i PCB-design?

1. Layout för strömspårning

- Korta och breda spår: Minimera resistans (R) och parasitisk induktans (L) för att minska spänningsfall och brus.

- Undvik parallell routning med signalspår: Förhindra att strömstörningar kopplas in i känsliga signaler (t.ex. klockor, analoga kretsar).

- Strategi för lager:

- I flerlagerkort ska hela lager ägnas åt ström- och jordplan.

- Kritiska strömskenor (t.ex. spänning i processorkärnan) bör ha särskilda strömförsörjningsstationer.

2. Filtrering av effekt

- Frikopplingskondensatorer:

- Bulkelektrolytkondensatorer (10-100 μF) vid strömingångar för att stabilisera spänningen.

- Små keramiska kondensatorer (0,1 μF) nära IC-stiften för att filtrera högfrekvent brus.

- LC-filter:

- Lägg till π-filter (kondensator + induktor) för bruskänsliga moduler (t.ex. PLL).

3. Strömförsörjning och jordning

- Returvägar med låg impedans:

- Använd solida jordplan; undvik delningar som orsakar impedansdiskontinuiteter.

- Flera vior för att ansluta ström- och jordplan (minskar viainduktansen).

- Stjärnjordning:

- Separera högeffekts- och känsliga kretsar med enpunktsjordning.

4. Simulering och validering

- PDN-analys (Power Delivery Network):

- Målets impedans: ( Z_{\text{mål}} = \frac{\Delta V}{\Delta I} ).

- Verktyg: ANSYS SIwave, Cadence Sigrity.

- Rippel- och brusprovning:

- Verifiera effektbrusnivåerna med oscilloskop eller simuleringar.

Hur integrerar man design för testbarhet (DFT) i PCB-design?

1. Testpunkter och gränssnitt

- Testpunkter för kritiska signaler:

- Tillhandahåll vias eller pads (diameter ≥1 mm, avstånd ≥2,54 mm) för probåtkomst.

- Märk testpunkterna (t.ex. TP1, TP2).

- Standardgränssnitt:

- Placera JTAG-, UART- eller SWD-gränssnitt nära kortets kanter.

2. Märkning av tavlan (silkscreen)

- Komponentmarkeringar:

- Märk ut referensbeteckningar (t.ex. R1, C2), polaritet (+/-) och Pin 1.

- Använd silkscreen med hög kontrast (vit/svart).

- Funktionella zoner:

- Avgränsa områden (t.ex. "Power Section") för enkel identifiering.

3. Programmerbar testteknik

- Boundary Scan (JTAG):

- IEEE 1149.1-kompatibla IC:er (t.ex. FPGA:er, MCU:er) möjliggör testning av sammankopplingar.

- Automatiserad testutrustning (ATE):

- Reservera gränssnitt för testfixturer (t.ex. pogostiftplattor).

4. Simulering och validering

- Kontroll av DFT-regler:

- Säkerställ testpunktstäckning (t.ex. >90% av tillgängliga nät).

- Analys av felläge:

- Validera testkretsar via SPICE-simuleringar.

Jämförelse av viktiga designprinciper

| Power Integrity (PI) | Design för testbarhet (DFT) |

|---|---|

| Lågimpedans strömfördelning | Tillgänglighet för fysisk testpunkt |

| Optimering av kopplingskondensator | Stöd för JTAG/boundary scan |

| Minimera kopplingen mellan effekt och signal | Tydlig märkning av komponenter/gränssnitt |

| PDN-simulering och ripple-analys | ATE-kompatibel design |

Exempel:

- PI-optimering: DDR4-minnets strömförsörjningsplan med flera 0805 0,1 μF-kapslar (målimpedans ≤0,1Ω).

- DFT-implementering: Industriellt styrkort med 20 testpunkter för automatiserad testning med flygande sond.

Genom att systematiskt ta itu med PI och DFT kan konstruktörerna förbättra effektprestanda, testeffektivitet och produktionstillförlitlighet.

Relaterade inlägg