How to Improve PCB Circuit Board Performance and Reliability?

Using a systematic approach to optimize the PCB design process can effectively improve the performance and reliability of PCB design and ensure the stable operation of electronic devices.

Table of Contents

Core Design Strategies & Innovative Practices

1. Precision Layout & Intelligent Routing

- Implement modular zoning with ≥5mm analog/digital isolation

- Apply 3W rule for high-speed components (spacing≥3×trace width)

- Thermal-aware chessboard placement with 0.5mm cooling via arrays

2. Advanced Power Delivery Network

- π-filter networks (100μF+0.1μF+10nF configuration)

- Power integrity simulation (target impedance<50mΩ@1MHz)

- Embedded capacitance technology (50nF/cm² density)

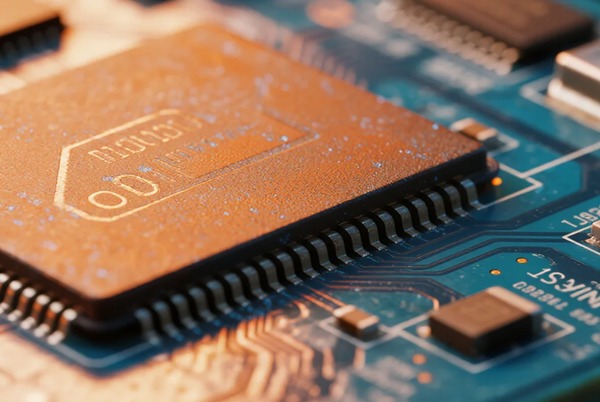

3. High-Speed Signal Integrity Solutions

- Differential pair control: ±2.5mil length matching

- Impedance control: ±10% tolerance (HSPICE-verified)

- Back-drilling technology (stub length<12mil)

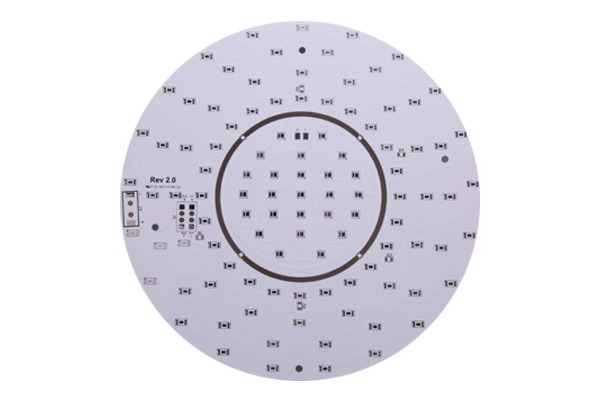

4. Thermal Management 4.0

- 3D thermal simulation (ΔT<15℃ target)

- Hybrid cooling systems:

- 2oz copper + thermal vias (φ0.3mm@1mm pitch)

- Selective heatsink attachment (>5W/mK)

5. EMI/EMC Defense Matrix

- Faraday cage shielding (>60dB@1GHz)

- Ferrite bead arrays (100Ω@100MHz)

- Segmented ground planes (crossings<λ/20)

Manufacturing Innovations

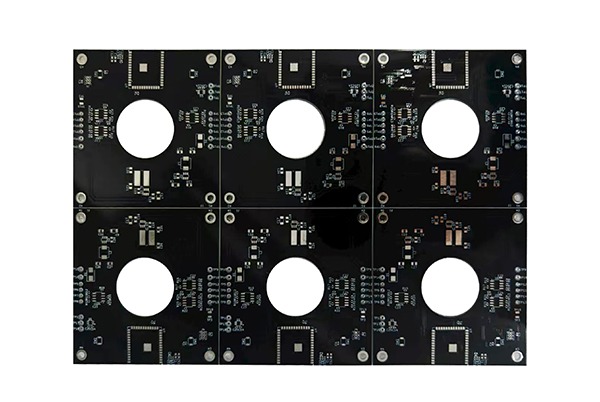

6. DFM 2.0 Standards

- HDI process controls:

- Laser microvias: φ75±15μm

- Layer alignment: ±25μm

- 3D-printed prototyping (24hr turnaround)

7. Smart Test Ecosystem

- JTAG boundary scan (>95% coverage)

- AI-driven test systems:

- Automated TDR (±1% resolution)

- Real-time thermal imaging (0.1℃ resolution)

Reliability Enhancements

8. Military-Grade Robustness

- HALT testing (6σ compliance)

- Nanocoating technology (300% improved protection)

- Self-healing circuits (MTBF>100,000hrs)

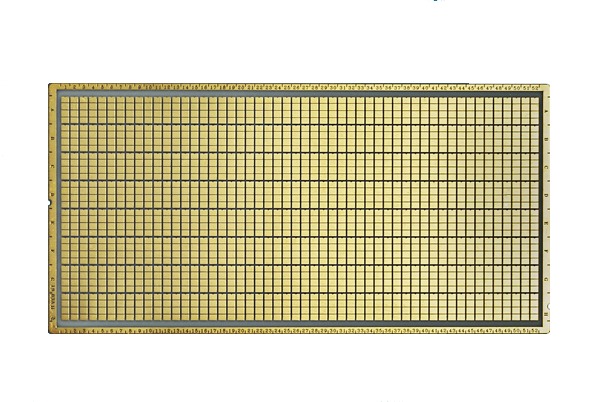

9. Next-Gen Stackup Architecture

- Hybrid material stackup:

- RF layers: Rogers 4350B (εr=3.48)

- Standard layers: High-Tg FR-4 (>170℃)

- Embedded component technology (40% integration boost)

Verification Methodology

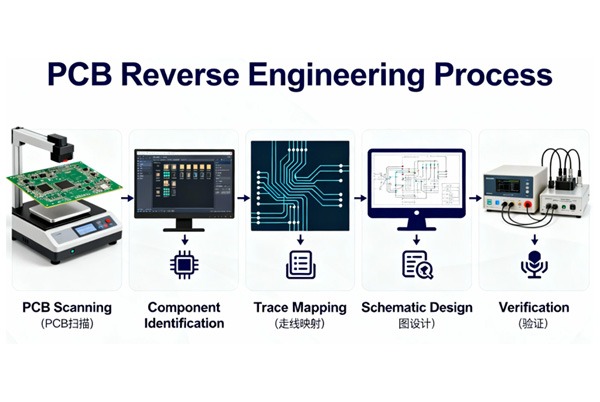

10. Full Lifecycle Validation

- Phase-gated verification:

- Pre-layout SI/PI simulation

- Prototype TDR testing

- Production HASS validation

- Digital twin modeling (>90% prediction accuracy)

Performance Benchmarking

| Design Parameter | Conventional | Optimized | Improvement |

|---|---|---|---|

| Signal Loss | 6dB@10GHz | 3dB@10GHz | 50% |

| Power Noise | 50mVpp | 15mVpp | 70% |

| Thermal Resistance | 35℃/W | 18℃/W | 48% |

| EMC Margin | 3dB | 10dB | 233% |

Industry Implementation Cases

5G Base Station Breakthroughs:

- 77GHz mmWave transmission

- <8mVrms power noise

- <8℃/cm² thermal gradient

EV Power Systems:

- 200A stacked busbars

- 150℃ continuous operation

- ISO 26262 ASIL-D certified

Related Posts