Entwurf und Herstellung von 16-Lagen-Leiterplattenstapeln

16-Lagen-Leiterplatten (PCBs) sind zu einem wichtigen Technologieträger für die komplexe Systemintegration geworden. Ihr Design und ihre Herstellung erfordern eine präzise Kontrolle der Zwischenlagen und ein Management der Signalintegrität. Diese mehrlagigen Leiterplatten bringen die Anforderungen an eine hohe Verdrahtungsdichte und die Signalintegrität durch eine präzise Laminatstruktur perfekt ins Gleichgewicht.

Inhaltsübersicht

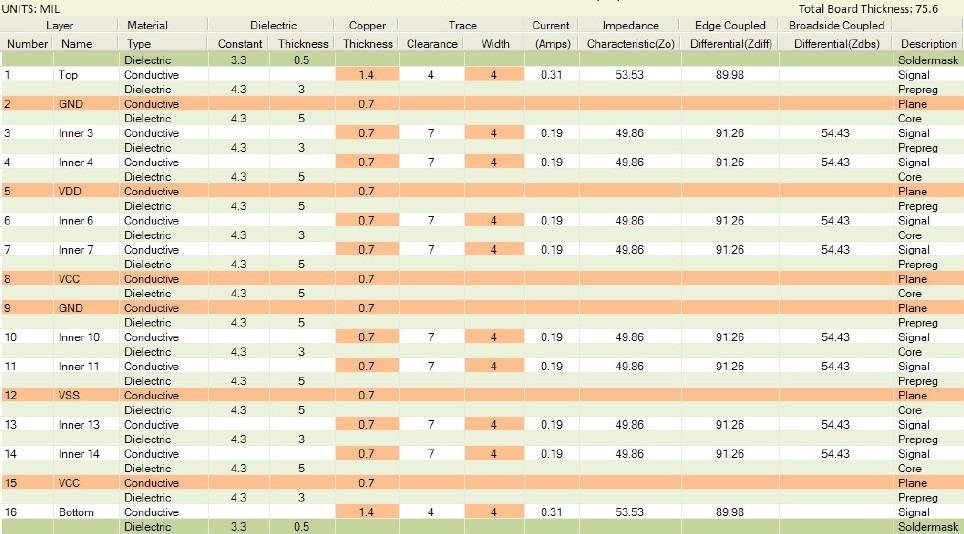

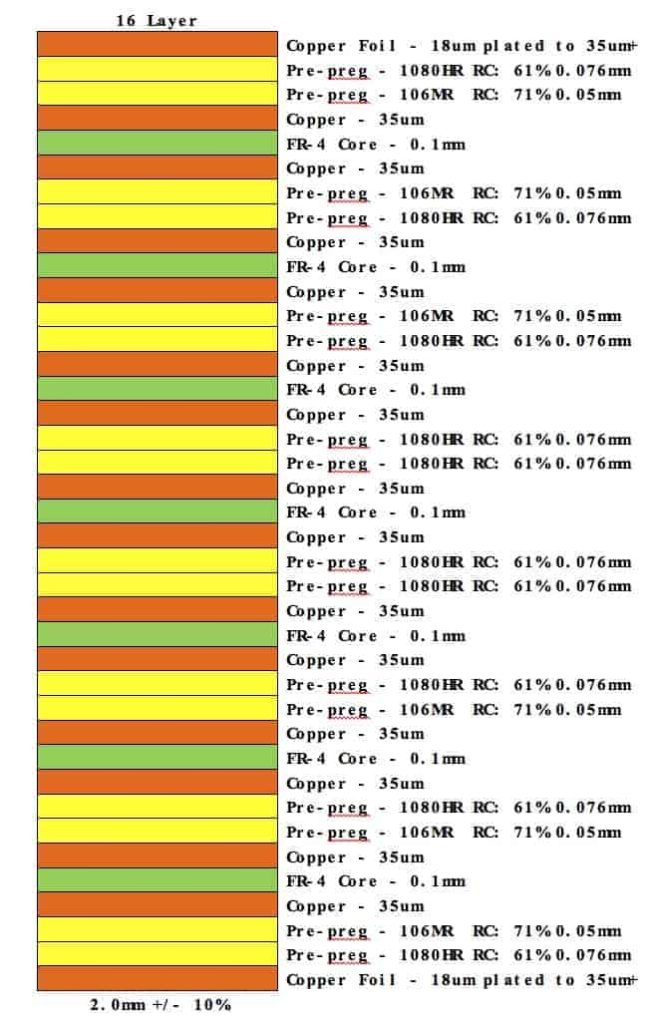

Typischer Laminataufbau einer 16-Lagen-Leiterplatte

Konfiguration 1: Optimiertes Hochgeschwindigkeitssignal (8S4P4G)

L1: Signal(TOP) L2: GND L3: Signal L4: Signal

L5: PWR1 L6: GND L7: Signal L8: Signal

L9: PWR2 L10:GND L11:Signal L12:Signal

L13:PWR3 L14:GND L15:Signal L16:GND(BOT)Vorteile:

- Jede Signalebene hat eine benachbarte Referenzebene

- Geteilte Leistungsebenen ermöglichen mehrere Spannungsdomänen

- Geeignet für serielle Hochgeschwindigkeitsverbindungen mit 56 Gbps+

Konfiguration 2: Mixed-Signal-Verarbeitungstyp

L1: RF-Signal L2: GND L3: Analog L4: PWR

L5: Digital L6: GND L7: Digital L8: PWR

L9: Digital L10:GND L11:Digital L12:PWR

L13:Analog L14:GND L15:RF L16:GNDEigenschaften:

- RF- und Analogschaltungen mit Perimeterabschirmung

- Digitale Signalführung auf inneren Schichten

- Ideal für medizinische Bildgebungsgeräte

Konfiguration 3: High-Power-Anwendungstyp

(einschließlich 2 Unzen dicker Kupfer-Leistungsschichten und spezieller Wärmeschichten)Wichtige Punkte:

- 3OZ dicke Leistungsschichten aus Kupfer

- Eingebettete Wärmeschichten mit Metallkern

- Entwickelt für EV-Wechselrichter

Empfehlung von Experten: Führen Sie 3D-Simulationen des elektromagnetischen Feldes durch, wenn Sie Stackup-Konfigurationen auswählen. Ansys HFSS oder CST Studio Suite werden für die Designvalidierung empfohlen.

Kritische Materialtechnologie und Dickenkontrolle

1. High-End-Materialauswahl

| Material Typ | Typisches Modell | Dk@10GHz | Df@10GHz | Anwendungen |

|---|---|---|---|---|

| Hochgeschwindigkeits-FR4 | Megtron6 | 3.7 | 0.002 | 112G SerDes |

| Verlustarmes Material | RO4835 | 3.5 | 0.003 | mmWave-Radar |

| Hoch-Tg-Material | IT-180A | 4.3 | 0.012 | Kfz-Elektronik |

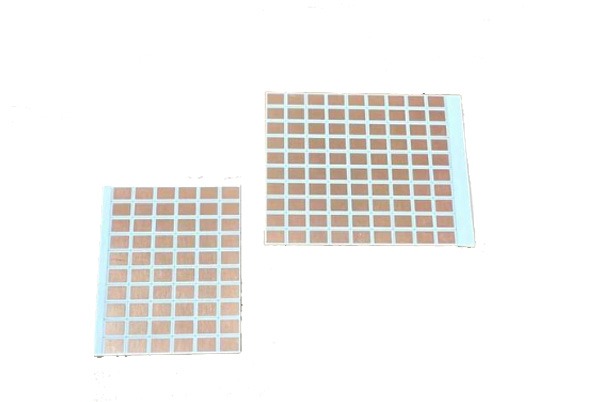

2.Dicken-Kontrollsystem

Beispiel für 1,6 mm Plattendicke:

- Signalschichtkupfer: 1OZ (35 μm)

- Kupfer der Stromschicht: 2OZ (70 μm)

- Dielektrische Dicke: 0,1mm (4mil)

- Prepreg: Typ 1080

- Impedanzkontrollschicht: 0,2mm(8mil)

Berechnungsformel:

Gesamtdicke = Σ(Kupferdicke) + Σ(Dielektrikumdicke) + Lötmaskendicke

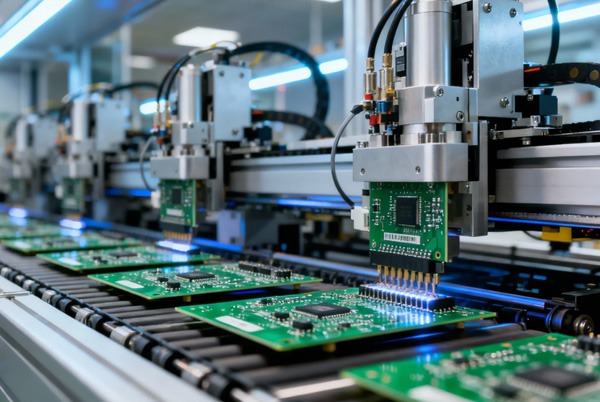

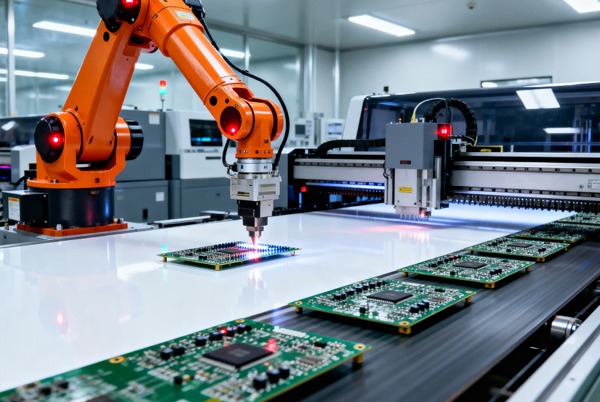

Fortschrittlicher Fertigungsprozessfluss

- Laser-Bohrtechnik:

- CO2-Laser: Löcher > 100 μm

- UV-Laser: Mikrobohrungen unter 100 μm

- Blind durch Seitenverhältnis: 1:0,8

- Puls-Plating-Verfahren:

- Lochkupferdicke: ≥25 μm

- Gleichmäßigkeit der Kupferoberfläche: ±3 μm

- Rückwärtsbohrgenauigkeit: ±50 μm

- Kritische Parameter für die Laminierung:

- Temperatur: 180 ± 5 °C

- Druck: 350PSI

- Dauer: 90 Minuten

- Vakuumniveau: <50 mbar

Normen für die Qualitätskontrolle:

- IPC-6012B Klasse 3

- IPC-A-600G

- 100% Flying Probe Test

- 3D-Röntgeninspektion

Entwurf der Signalintegrität

- Drei Elemente der Impedanzkontrolle:

- Linienbreitentoleranz ±10 %

- Toleranz der dielektrischen Dicke ±7 %

- Kupferdicke Toleranz ±1μm

- Power Integrity Design:

- Ebenenkapazität > 500 pF/in²

- Platzierung von Entkopplungskondensatoren:

- 0,1 μF@0402 pro BGA

- 10 μF@0603 pro Spannungsbereich

- EMC-Optimierungsstrategien:

- Kantenschutz-Durchkontaktierungen: Abstand <λ/20

- Isolationsschlitze: Breite > 50 mil

- Sandwich-Bodenstruktur

Fallstudie: Eine 5G-Basisstation AAU mit 16-Lagen-Leiterplatten erzielte eine um 32 % geringere Einfügedämpfung, eine um 28 % bessere thermische Leistung und eine MTBF-Zuverlässigkeit von 100.000 Stunden.

Empfohlene professionelle Fertigungsdienstleistungen

Topfast Angebote Premium 16-Layer PCB Turnkey-Lösungen:

✅ Bis zu 32-lagiger kundenspezifischer Lagenaufbau

✅ ±5 % Impedanzregelung

✅ 100 μm Laser-Blind-Durchkontaktierungen

✅ 3D-gedruckte Rapid-Prototypen

✅ Umfassende SI/PI-Simulationsdienstleistungen

Sofortiges individuelles Angebot anfordern: Technische Anforderungen einreichen

FQA-Höhepunkte

F: Wie können Kosten und Leistung in 16-Schicht-Designs ausgeglichen werden?

A: Empfohlene “4+8+4” Hybrid-Laminierung: 4 Hochgeschwindigkeits-Materialschichten + 8 FR4-Schichten reduzieren die Kosten um 15 %, während die Leistung der kritischen Signalschichten erhalten bleibt.

F: Wie lassen sich thermische Herausforderungen bei 16-Lagen-Platinen bewältigen?

A: Drei wirksame Lösungen:

- Eingebettete Kupferblöcke für lokale Kühlung

- Thermische Durchgangs-Arrays

- Verbundwerkstoffe mit Metallkern

F: Häufige Fehler bei der Massenproduktion von 16-Lagen-Platten?

A: Schwerpunktbereiche:

- Versatz von Schicht zu Schicht

- Kupferrisse in Durchkontaktierungen

- Hohlräume in dielektrischen Schichten

- Ungleichmäßige Oberflächenbeschaffenheit

Anwendungen von 16-Layer PCBs

16-Lagen-Leiterplatten schaffen durch präzise Stapelstrukturen ein perfektes Gleichgewicht zwischen den Anforderungen an eine hohe Routingdichte und die Signalintegrität und finden daher in vielen Bereichen Anwendung:

- 5G-Kommunikationsinfrastruktur: Basisstationsausrüstungen, die Millimeterwellenübertragung und Massive-MIMO-Technologie unterstützen

- Hochleistungs-ComputingProzessor-Verbindungen für KI-Server und Supercomputer

- Medizinische Bildgebungsgeräte: Kontrollsysteme für CT, MRI und andere moderne medizinische Geräte

- Luft- und Raumfahrtelektronik: Zuverlässige Lösungen für Satellitenkommunikation und Flugkontrollsysteme

- Kfz-ElektronikDomänencontroller für autonomes Fahren und intelligente Cockpitsysteme

Typische technische Parameter:

- Plattendicke: 1,6-2,4 mm (anpassbar)

- Mindestlinienbreite/-abstand: 3/3mil (0,075/0,075mm)

- Minimale Apertur:0,15 mm (Laserbohren)

- Ausrichtungstoleranz zwischen den Schichten: ±25 μm

- Impedanzregelungsgenauigkeit: ±7 %

Einblicke in die Industrie: Mit der Einführung von PCIe 5.0- und DDR5-Technologien wächst der Markt für 16-Layer-Leiterplatten jährlich um 12 % und wird voraussichtlich bis 2025 weltweit 5,8 Mrd. USD übersteigen.

Konsultieren Sie jetzt unsere Experten: 16-Layer PCB White Paper herunterladen

Verwandte Leseempfehlungen

4-lagige flexible Leiterplatte

Verwandte Beiträge