Häufige Probleme bei der Verbesserung der PCB-Zuverlässigkeit

Inhaltsübersicht

Wie berechnet man die PCB-Impedanz?

Die Berechnung der Leiterplattenimpedanz gewährleistet die Signalintegrität, insbesondere bei Hochgeschwindigkeits- und RF-Schaltungen.

1. PCB Stackup & Geometrie bestimmen

- Anzahl der Schichten: Einfach, doppelt oder mehrlagig.

- Spurbreite (W) und Dicke (T): Entscheidend für die Impedanzkontrolle.

- Dielektrische Dicke (H): Abstand zwischen Signalebene und Bezugsebene (z. B. Erde).

- Gewicht von Kupfer: Normalerweise 0,5 Unzen (17,5 µm) bis 2 Unzen (70 µm).

2. Identifizierung der Dielektrizitätskonstante (Dk oder εᵣ)

- FR-4: ~4,3-4,8 (variiert mit der Frequenz).

- Rogers RO4003C: ~3,38 (verlustarm für RF).

- Polyimid: ~3,5 (flexible Leiterplatten).

- Hinweis: Dk nimmt bei höheren Frequenzen leicht ab.

3. Impedanzberechnungsmethode wählen

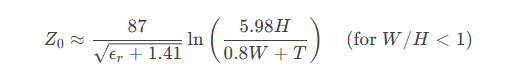

Microstrip (Leiterbahn der äußeren Schicht über der Grundplatte):

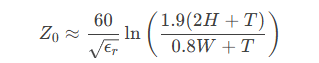

Stripline (innere Schicht zwischen zwei Masseebenen):

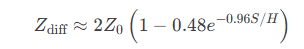

Differential-Paar: Erfordert einen Abstand (S) zwischen den Leiterbahnen.

4. Verwenden Sie Impedanzrechner oder Tools

- Online-Tools: Saturn PCB Toolkit, EEWeb-Rechner.

- PCB-Software: Altium Designer, KiCad oder Cadence verfügen über eingebaute Impedanzberechner.

- EM-Simulatoren: Ansys HFSS, CST (für fortgeschrittene Entwürfe).

5. Optimieren Sie das Design anhand der Ergebnisse

- Anpassen Leiterbahnbreite (↑ Breite → ↓ Impedanz).

- Ändern Sie dielektrische Dicke (↑ H → ↑ Impedanz).

- zwicken Leiterbahnabstände für Differentialpaare.

- Wählen Sie Materialien mit entsprechendem Dk (z. B. Rogers für RF).

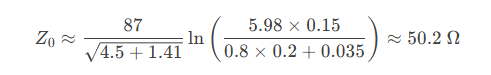

Berechnungsbeispiel (FR-4 Microstrip)

Gegeben:

- Leiterbahnbreite (W) = 0,2 mm

- Dielektrische Dicke (H) = 0,15 mm

- Dicke des Kupfers (T) = 0,035 mm

- εᵣ = 4,5

Verwendung der Mikrostreifenformel:

Entspricht der Standardimpedanz von 50Ω für HF-Signale.

Wie man die Signalintegrität bei PCB-Design?

1. Layout Entwurf

Bei der Gestaltung des Leiterplattenlayouts ist es wichtig, die Anordnung von Signal-, Stromversorgungs- und Masseleitungen zu berücksichtigen und Störungen zu vermeiden, die durch die Kreuzung von Signal-, Stromversorgungs- und Masseleitungen verursacht werden. Außerdem ist es wichtig, die Länge der Signalleitungen zu minimieren, um Übersprechen und Verzögerungen zu reduzieren.

2. Impedanzanpassung

Beim Entwurf von Hochgeschwindigkeits-Signalleitungen muss eine Impedanzanpassung vorgenommen werden, um sicherzustellen, dass die Impedanz der Signalleitungen mit der Impedanz der Signalquelle und der Last übereinstimmt und somit Signalreflexionen und Übersprechen vermieden werden.

3. Signalleitungsführung

Beim Leiterplattendesign wirkt sich auch die Verlegung der Signalleitungen auf die Signalintegrität aus und muss bestimmten Regeln folgen. So sollten beispielsweise differentielle Signalleitungen einen bestimmten Abstand einhalten und parallel verlegt werden, während Single-Ended-Signalleitungen parallel zu Masseleitungen verlegt werden sollten und Signalleitungsbiegungen minimiert werden sollten.

4. Strom und Erdung

Beim Leiterplattendesign wirkt sich auch das Design von Stromversorgung und Erdung auf die Signalintegrität aus. Es sollte eine stabile Stromversorgung und Erdung verwendet werden, und der Widerstand und die Induktivität der Stromversorgung und Erdung sollten so weit wie möglich minimiert werden.

5. Simulation Verifizierung

Nach Fertigstellung des PCB-Designs ist eine Simulationsprüfung erforderlich, um sicherzustellen, dass die Signalintegrität den Anforderungen entspricht. Durch die Simulation können Probleme wie Signalverzögerung, Reflexion und Nebensprechen erkannt und das PCB-Design optimiert werden.

Wie wird die elektromagnetische Verträglichkeit (EMC) beim PCB-Design berücksichtigt?

1. PCB-Layout für EMC

- Paralleles Routing minimieren: Vermeiden Sie lange Parallelführungen zwischen Signal- und Stromversorgungs-/Masseleitungen, um Übersprechen und elektromagnetische Einkopplung zu reduzieren.

- Isolierung kritischer Signale: Trennen Sie Hochgeschwindigkeitssignale (z. B. Uhren, HF) und empfindliche Analogsignale von verrauschten Schaltungen (z. B. Schaltnetzteilen).

- Layer Stackup Strategie:

- Verwenden Sie zur Abschirmung solide Masseflächen in der Nähe der Signalebenen.

- Führen Sie Hochgeschwindigkeitssignale auf den inneren Schichten zwischen den Masseebenen zur Eindämmung.

2. Erdungstechniken

- Niedrig-Impedanz-Groundplanes: Verwenden Sie ununterbrochene Masseflächen, um Masseschleifen zu minimieren und die Strahlungsemissionen zu reduzieren.

- Sorgfältige Aufteilung des Bodens: Trennen Sie die analoge/digitale Masse nur bei Bedarf mit einem einzigen Anschlusspunkt (z. B. Ferritperle oder 0Ω-Widerstand).

- Über Stitching: Platzieren Sie mehrere Massedurchführungen um hochfrequente Leiterbahnen oder Platinenränder, um Hohlraumresonanzen zu unterdrücken.

3. Filterung und Unterdrückung

- Ferrit-Perlen: Wird den Strom-/IO-Leitungen hinzugefügt, um hochfrequentes Rauschen zu blockieren.

- Entkopplungskondensatoren: In der Nähe der IC-Stromversorgungspins platzieren (z. B. 0,1μF + 1μF), um Hoch- und Mittelfrequenzrauschen zu filtern.

- Gleichtaktdrosseln: Verwendung bei differentiellen Paaren (z. B. USB, Ethernet) zur Unterdrückung von Gleichtaktstrahlung.

4. Abschirmung und Schnittstellengestaltung

- Kabelabschirmung: Verwenden Sie abgeschirmte Anschlüsse (z. B. USB, HDMI) mit 360°-Erdung zum Gehäuse.

- Abschirmung auf Board-Ebene: Fügen Sie Metalldosen oder leitende Beschichtungen über empfindliche RF-Schaltungen hinzu.

- Kantenschutz: Führen Sie empfindliche Leiterbahnen von den Platinenrändern weg; verwenden Sie Schutzleiterbahnen oder geerdeten Kupferguss um sie herum.

5. Simulation und Prüfung

- Vor-Layout-Analyse: Verwenden Sie Tools wie ANSYS HFSS oder CST, um Strahlungs-Hotspots zu modellieren.

- Post-Layout-Verifizierung:

- Führen Sie Nahfeld-Scans durch, um Emissionsquellen zu identifizieren.

- Durchführung von Konformitätsprüfungen (z. B. FCC, CE) für gestrahlte/geleitete Emissionen.

- Entwurf Iteration: Optimieren Sie auf der Grundlage der Testergebnisse (z. B. Hinzufügen von Abschlusswiderständen oder Anpassen der Leiterbahnabstände).

Beispiel-Fixes:

- Ein 100-MHz-Taktgeber strahlt übermäßig stark ab: Fügen Sie Abschlusswiderstände in Reihe hinzu oder verlegen Sie die Leitung zwischen Masseebenen.

- Rauschen der Schaltnetzteile: π-Filter (LC) am Eingang/Ausgang einsetzen.

Durch die Integration dieser Verfahren können Leiterplatten die EMV-Normen (z. B. IEC 61000) erfüllen und gleichzeitig kostspielige Umgestaltungen minimieren. Testen Sie immer frühzeitig Prototypen!

Wie berücksichtigt man Power Integrity (PI) beim PCB-Design?

1. Power Trace Layout

- Kurze und breite Spuren: Minimieren Sie Widerstand (R) und parasitäre Induktivität (L), um Spannungsabfall und Rauschen zu reduzieren.

- Paralleles Routing mit Signalverläufen vermeiden: Verhindert die Einkopplung von Leistungsstörungen in empfindliche Signale (z. B. Uhren, analoge Schaltungen).

- Ebene Strategie:

- Bei Multilayer-Platinen sollten Sie ganze Lagen für Stromversorgungs- und Erdungsebenen reservieren.

- Kritische Stromschienen (z. B. die CPU-Kernspannung) sollten über eigene Stromversorgungsebenen verfügen.

2. Leistungsfilterung

- Entkopplungskondensatoren:

- Großvolumige Elektrolytkondensatoren (10-100μF) an den Leistungseingängen zur Stabilisierung der Spannung.

- Kleine Keramikkondensatoren (0,1μF) in der Nähe der IC-Pins, um hochfrequente Störungen zu filtern.

- LC-Filter:

- Hinzufügen von π-Filtern (Kondensator + Induktor) für rauschempfindliche Module (z. B. PLLs).

3. Strom und Erdung

- Niederohmige Rückkanäle:

- Verwenden Sie solide Masseflächen; vermeiden Sie Spalten, die Impedanzdiskontinuitäten verursachen.

- Mehrere Durchkontaktierungen zur Verbindung von Stromversorgungs- und Erdungsebenen (reduziert die Induktivität der Durchkontaktierung).

- Sternförmige Erdung:

- Getrennte Stromkreise mit hoher Leistung und empfindlichen Schaltkreisen, mit Ein-Punkt-Erdung.

4. Simulation und Validierung

- PDN (Power Delivery Network) Analyse:

- Zielimpedanz: ( Z_{\text{target}} = \frac{\Delta V}{\Delta I} ).

- Werkzeuge: ANSYS SIwave, Cadence Sigrity.

- Prüfung auf Restwelligkeit und Rauschen:

- Überprüfen Sie die Leistungsrauschpegel mit Oszilloskopen oder Simulationen.

Wie kann man Design for Testability (DFT) in das PCB-Design einbeziehen?

1. Prüfpunkte und Schnittstellen

- Kritische Signalprüfpunkte:

- Sehen Sie Durchkontaktierungen oder Pads (Durchmesser ≥1mm, Abstand ≥2,54mm) für den Zugang zur Sonde vor.

- Beschriften Sie die Prüfpunkte (z. B. TP1, TP2).

- Standard-Schnittstellen:

- Platzieren Sie JTAG-, UART- oder SWD-Schnittstellen in der Nähe der Platinenränder.

2. Kartonbeschriftung (Siebdruck)

- Bauteil-Kennzeichnungen:

- Kennzeichnen Sie die Referenzbezeichner (z. B. R1, C2), die Polarität (+/-) und Pin 1.

- Verwenden Sie einen kontrastreichen Siebdruck (weiß/schwarz).

- Funktionale Zonen:

- Gliedern Sie die Bereiche (z. B. "Power Section") zur einfachen Identifizierung.

3. Programmierbare Prüftechniken

- Boundary Scan (JTAG):

- IEEE 1149.1-konforme ICs (z. B. FPGAs, MCUs) ermöglichen Verbindungstests.

- Automatisierte Prüfgeräte (ATE):

- Reservieren Sie Schnittstellen für Prüfvorrichtungen (z. B. Pogo-Pins).

4. Simulation und Validierung

- DFT-Regelkontrollen:

- Sicherstellung der Testpunktabdeckung (z. B. >90% der zugänglichen Netze).

- Fehlermodus-Analyse:

- Validierung von Testschaltungen durch SPICE-Simulationen.

Vergleich der wichtigsten Gestaltungsprinzipien

| Leistungsintegrität (PI) | Entwurf für Testbarkeit (DFT) |

|---|---|

| Leistungsverteilung mit niedriger Impedanz | Zugänglichkeit des physischen Prüfpunkts |

| Optimierung des Entkopplungskondensators | Unterstützung von JTAG/Boundary Scan |

| Minimierung der Leistungs-Signal-Kopplung | Klare Beschriftung der Komponenten/Schnittstellen |

| PDN-Simulation und Restwelligkeitsanalyse | ATE-kompatible Ausführung |

Beispiele:

- PI-Optimierung: DDR4-Speicher-Powerplanes mit mehreren 0805 0,1μF-Caps (Zielimpedanz ≤0,1Ω).

- DFT-Implementierung: Industrielle Steuerplatine mit 20 Prüfpunkten für automatisierte Flying-Probe-Tests.

Durch die systematische Berücksichtigung von PI und DFT können Entwickler die Leistung, die Testeffizienz und die Produktionszuverlässigkeit verbessern.

Verwandte Beiträge