Problèmes courants liés à l'amélioration de la fiabilité des circuits imprimés

Table des matières

Comment calculer l'impédance d'un circuit imprimé ?

Le calcul de l'impédance des circuits imprimés garantit l'intégrité des signaux, en particulier pour les circuits à grande vitesse et les circuits RF.

1. Déterminer l'empilement et la géométrie des circuits imprimés

- Nombre de couches: Simple, double ou multicouche.

- Largeur de la trace (W) et épaisseur (T): Essentiel pour le contrôle de l'impédance.

- Epaisseur du diélectrique (H): Distance entre la couche de signal et le plan de référence (par exemple, la terre).

- Poids de cuivre: Généralement de 0,5 oz (17,5 µm) à 2 oz (70 µm).

2. Identifier la constante diélectrique (Dk ou εᵣ)

- FR-4: ~4,3-4,8 (varie selon la fréquence).

- Rogers RO4003C: ~3,38 (faible perte pour RF).

- Polyimide: ~3,5 (circuits imprimés souples).

- Note: Dk diminue légèrement à des fréquences plus élevées.

3. Choisir la méthode de calcul de l'impédance

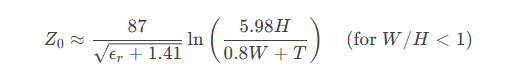

Microruban (trace de la couche externe sur le plan de masse) :

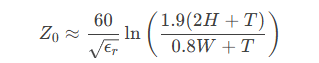

Ligne de démarcation (couche interne entre deux plans de masse) :

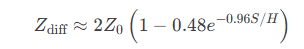

Paire différentielle: Nécessite un espacement (S) entre les traces.

4. Utiliser des calculateurs ou des outils d'impédance

- Outils en ligne: Saturn PCB Toolkit, EEWeb Calculator.

- Logiciel PCB: Altium Designer, KiCad ou Cadence intègrent des calculateurs d'impédance.

- Simulateurs EM: Ansys HFSS, CST (pour les conceptions avancées).

5. Optimiser la conception en fonction des résultats

- Ajuster largeur de la trace (↑ largeur → ↓ impédance).

- Modifier épaisseur du diélectrique (↑ H → ↑ impédance).

- Modifier espacement des traces pour les paires différentielles.

- Sélectionner matériaux avec les Dk appropriés (par exemple, Rogers pour RF).

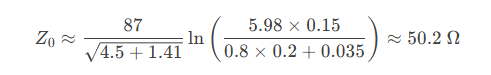

Exemple de calcul (FR-4 Microstrip)

Compte tenu de ce qui précède :

- Largeur de la trace (W) = 0,2 mm

- Epaisseur du diélectrique (H) = 0,15 mm

- Épaisseur du cuivre (T) = 0,035 mm

- εᵣ = 4,5

En utilisant la formule microstrip :

Correspond à l'impédance standard de 50Ω pour les signaux RF.

Comment prendre en compte l'intégrité du signal dans Conception de circuits imprimés?

1. Conception de la mise en page

Dans la conception des circuits imprimés, il est important de tenir compte de la disposition des lignes de signaux, des lignes électriques et des lignes de terre, et d'éviter les interférences causées par le croisement des lignes de signaux, des lignes électriques et des lignes de terre. En outre, il est essentiel de minimiser la longueur des lignes de signaux afin de réduire la diaphonie et le retard.

2. Adaptation d'impédance

Lors de la conception de lignes de signaux à grande vitesse, l'adaptation d'impédance doit être effectuée pour garantir que l'impédance des lignes de signaux correspond à l'impédance de la source de signaux et de la charge, évitant ainsi la réflexion des signaux et la diaphonie.

3. Acheminement des lignes de signalisation

Dans la conception des circuits imprimés, le routage des lignes de signaux affecte également l'intégrité des signaux et doit suivre certaines règles. Par exemple, les lignes de signaux différentiels doivent respecter un certain espacement et être acheminées en parallèle, tandis que les lignes de signaux asymétriques doivent être acheminées parallèlement aux lignes de masse, et les courbures des lignes de signaux doivent être réduites au minimum.

4. Alimentation et mise à la terre

Dans la conception des circuits imprimés, la conception de l'alimentation et de la mise à la terre affecte également l'intégrité du signal. Il convient d'utiliser une alimentation et une mise à la terre stables et de réduire autant que possible la résistance et l'inductance de l'alimentation et de la mise à la terre.

5. Vérification de la simulation

Une fois la conception du circuit imprimé achevée, une vérification par simulation est nécessaire pour s'assurer que l'intégrité du signal répond aux exigences. La simulation permet de détecter des problèmes tels que le retard des signaux, la réflexion et la diaphonie, et d'optimiser la conception de la carte de circuit imprimé.

Comment prendre en compte la compatibilité électromagnétique (CEM) dans la conception des circuits imprimés ?

1. Disposition des circuits imprimés pour la CEM

- Minimiser l'acheminement parallèle: Évitez les longs tracés parallèles entre les signaux et les circuits d'alimentation/de masse afin de réduire la diaphonie et le couplage électromagnétique.

- Isolation des signaux critiques: Séparer les signaux analogiques sensibles et à grande vitesse (par exemple, horloges, RF) des circuits bruyants (par exemple, alimentations à découpage).

- Stratégie d'empilement des couches:

- Utiliser des plans de masse solides adjacents aux couches de signaux pour assurer le blindage.

- Acheminer les signaux à grande vitesse sur les couches internes entre les plans de masse pour les contenir.

2. Techniques de mise à la terre

- Plans de masse à faible impédance: Utilisez des plans de masse ininterrompus pour minimiser les boucles de masse et réduire les émissions par rayonnement.

- Séparer les terrains avec soin: Séparer les masses analogiques/numériques uniquement lorsque cela est nécessaire, avec un seul point de connexion (par exemple, une perle de ferrite ou une résistance de 0Ω).

- Via Stitching: Placez plusieurs vias de masse autour des traces à haute fréquence ou des bords de la carte pour supprimer les résonances de la cavité.

3. Filtrage et suppression

- Perles de ferrite: Ajouter aux lignes d'alimentation/IO pour bloquer les bruits à haute fréquence.

- Condensateurs de découplage: Placer près des broches d'alimentation du circuit intégré (par exemple, 0,1μF + 1μF) pour filtrer les bruits de haute et moyenne fréquence.

- Selfs de mode commun: Utilisation sur des paires différentielles (par exemple, USB, Ethernet) pour supprimer le rayonnement en mode commun.

4. Blindage et conception de l'interface

- Blindage du câble: Utilisez des connecteurs blindés (par exemple, USB, HDMI) avec une mise à la terre à 360° sur le châssis.

- Blindage au niveau de la carte: Ajouter des boîtes métalliques ou des revêtements conducteurs sur les circuits RF sensibles.

- Protection des bords: Éloignez les traces sensibles des bords de la carte ; utilisez des traces de protection ou des bandes de cuivre mises à la terre autour d'elles.

5. Simulation et essais

- Analyse préalable à la mise en page: Utilisez des outils tels que ANSYS HFSS ou CST pour modéliser les points chauds du rayonnement.

- Vérification après la mise en page:

- Effectuer des balayages en champ proche pour identifier les sources d'émission.

- Effectuer des tests de conformité (par exemple, FCC, CE) pour les émissions rayonnées/conduites.

- Itération de la conception: Optimiser en fonction des résultats des tests (par exemple, ajouter des résistances de terminaison ou ajuster l'espacement des traces).

Exemples de corrections:

- Une horloge de 100 MHz rayonne de manière excessive : Ajoutez des résistances de terminaison en série ou acheminez-la entre des plans de masse.

- Bruit de l'alimentation à découpage : mettre en place des filtres π (LC) à l'entrée et à la sortie.

En intégrant ces pratiques, les circuits imprimés peuvent répondre aux normes CEM (par exemple, CEI 61000) tout en minimisant les reconceptions coûteuses. Prototypez et testez toujours très tôt !

Comment prendre en compte l'intégrité de l'alimentation (PI) dans la conception des circuits imprimés ?

1. Disposition du tracé de puissance

- Traces courtes et larges: Minimiser la résistance (R) et l'inductance parasite (L) pour réduire la chute de tension et le bruit.

- Éviter le routage parallèle avec les tracés de signaux: Empêcher le bruit de puissance de se coupler à des signaux sensibles (par exemple, horloges, circuits analogiques).

- Stratégie en matière de couches:

- Dans les cartes multicouches, consacrer des couches entières aux plans d'alimentation et de masse.

- Les rails d'alimentation critiques (par exemple, la tension du cœur du processeur) doivent avoir des plans d'alimentation dédiés.

2. Filtrage de l'énergie

- Condensateurs de découplage:

- Condensateurs électrolytiques en vrac (10-100μF) aux entrées d'alimentation pour stabiliser la tension.

- Petits condensateurs en céramique (0,1μF) près des broches du circuit intégré pour filtrer le bruit à haute fréquence.

- Filtres LC:

- Ajouter des filtres π (condensateur + inductance) pour les modules sensibles au bruit (par exemple, les PLL).

3. Alimentation et mise à la terre

- Chemins de retour à faible impédance:

- Utiliser des plans de masse solides ; éviter les séparations qui provoquent des discontinuités d'impédance.

- Plusieurs vias pour relier les plans d'alimentation et de masse (réduction de l'inductance des vias).

- Mise à la terre en étoile:

- Séparer les circuits de haute puissance et les circuits sensibles, avec une mise à la terre en un seul point.

4. Simulation et validation

- Analyse du PDN (Power Delivery Network):

- Impédance de la cible : ( Z_{text{target}} = \frac{\Delta V}{\Delta I} ).

- Outils : ANSYS SIwave, Cadence Sigrity.

- Test d'ondulation et de bruit:

- Vérifier les niveaux de bruit de puissance à l'aide d'oscilloscopes ou de simulations.

Comment intégrer la conception pour la testabilité (DFT) dans la conception des circuits imprimés ?

1. Points d'essai et interfaces

- Points d'essai des signaux critiques:

- Prévoir des vias ou des plots (diamètre ≥1mm, espacement ≥2,54mm) pour l'accès aux sondes.

- Étiqueter les points de test (par exemple, TP1, TP2).

- Interfaces standard:

- Placer les interfaces JTAG, UART ou SWD près des bords de la carte.

2. Étiquetage du tableau (sérigraphie)

- Marquage des composants:

- Étiqueter les désignateurs de référence (par exemple, R1, C2), la polarité (+/-) et la broche 1.

- Utiliser une sérigraphie à fort contraste (blanc/noir).

- Zones fonctionnelles:

- Délimiter les zones (par exemple, "Section de l'alimentation") pour faciliter leur identification.

3. Techniques d'essai programmables

- Balayage de frontière (JTAG):

- Les circuits intégrés conformes à la norme IEEE 1149.1 (par exemple, FPGA, MCU) permettent de tester les interconnexions.

- Équipements d'essai automatisés (ATE):

- Réserver les interfaces des montages d'essai (par exemple, les plaques à broches pogo).

4. Simulation et validation

- Contrôles des règles DFT:

- Assurer la couverture des points de test (par exemple, >90% des réseaux accessibles).

- Analyse des modes de défaillance:

- Valider les circuits d'essai par des simulations SPICE.

Comparaison des principes clés de conception

| Intégrité de l'alimentation (PI) | Conception pour la testabilité (DFT) |

|---|---|

| Distribution d'énergie à faible impédance | Accessibilité du point d'essai physique |

| Optimisation du condensateur de découplage | Prise en charge du JTAG/balayage frontal |

| Minimiser le couplage puissance-signal | Étiquetage clair des composants/interfaces |

| Simulation PDN et analyse de l'ondulation | Conception compatible ATE |

Exemples:

- Optimisation de l'IP: Plans d'alimentation de la mémoire DDR4 avec plusieurs capuchons 0805 0,1μF (impédance cible ≤0,1Ω).

- Mise en œuvre de la DFT: Carte de contrôle industrielle avec 20 points de test pour des tests automatisés à l'aide de sondes volantes.

En abordant systématiquement l'IP et la DFT, les concepteurs peuvent améliorer les performances énergétiques, l'efficacité des tests et la fiabilité de la production.

Articles connexes