Estratégia de seleção de camadas de PCB

No desenvolvimento de produtos eletrônicos, a escolha da contagem de camadas de PCB é uma decisão crítica que afeta o sucesso ou o fracasso de um projeto. De acordo com Topfast’ s estatísticas de análise de big data, aproximadamente 38% do retrabalho de design de PCB é devido ao planejamento inicial inadequado da camada. Como fazer a melhor escolha com base nos requisitos do projeto é muito importante.

Índice

Comparação de camadas de PCB de 1 a 16+ camadas

1. PCBs de camada única

Anatomia estrutural

- Construção de base: FR-4 substrato + folha de cobre de um lado (35/70μm)

- Espessura típica: 1,6 mm (personalizável 0,8-2,4 mm)

- Acabamento da superfície: Mais frequentemente HASL (sem chumbo)

Principais vantagens

Custo mais baixo (40-50% mais barato do que a camada dupla)

A prototipagem rápida 24 horas por dia está amplamente disponível

Mais fácil de soldar/reparar manualmente

Limitações de desempenho

Densidade de encaminhamento <0,3m/cm² (limitada por jumpers)

Fraca integridade do sinal (ΔIL>3dB/polegada@1GHz)

Sem proteção EMI (>60% de risco de radiação)

Aplicações clássicas

- Eletrónica de consumo: Balanças, controlos remotos

- Sistemas de iluminação:Controladores LED

- Controlos industriais básicos:Módulos de relé

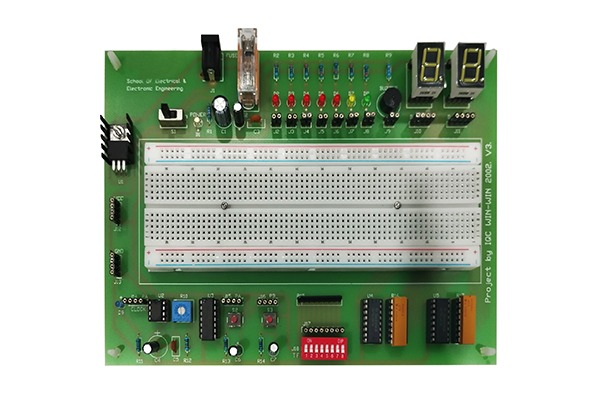

2. PCBs de camada dupla

Evolução técnica

- Tipos de via: PTH (chapeado) vs NPTH (mecânico)

- Capacidades modernas:Suporta traço/espaço de 4/4mil

- Controlo da impedância: tolerância de ±15% alcançável

Vantagens da conceção

Densidade de encaminhamento 2-3× superior (em comparação com a camada única)

Controlo básico da impedância (estrutura microstrip)

Desempenho EMC moderado (melhoria de 20 dB em relação à camada única)

Análise de custos

- Custo do material: +50% (vs. camada única)

- Prazo de entrega do protótipo:+1 dia útil

- Projectos complexos:Pode exigir resistências de ligação em ponte

Aplicações típicas

- Eletrónica automóvel:Unidades de controlo ECU

- Dispositivos IoT:Pontos finais Wi-Fi

- Controlos industriais:Módulos de E/S PLC

Consulte um engenheiro profissional para simplificar o seu projeto

3. PCBs de quatro camadas

Estrutura óptima de empilhamento

- Topo (sinal)

- GND (plano sólido)

- Potência (plano dividido)

- Fundo (sinal)

Inovações de desempenho

40% menos diafonia (vs. camada dupla)

Impedância de alimentação <100mΩ (com desacoplamento adequado)

Suporta barramentos de alta velocidade como DDR3-1600

Impacto nos custos

- Custo do material: +80% (vs dupla camada)

- Complexidade de conceção:Requer simulação SI

- Prazo de produção:+2-3 dias

Aplicações topo de gama

- Dispositivos médicos: Sondas de ultra-sons

- Câmaras industriais: processamento de 2MP

- ADAS para automóveis: Módulos de radar

4.PCB de seis camadas

Configurações típicas

6 camadas: S-G-S-P-S-G (melhor EMI)

8 camadas:S-G-S-P-P-S-G-S

12 camadas:G-S-S-G-P-P-G-S-S-G-P

Vantagens técnicas

Suporta sinais de alta velocidade de 10Gbps+

Integridade de potência (impedância PDN <30mΩ)

300% mais canais de encaminhamento (vs 4 camadas)

Considerações sobre os custos

- 6 camadas: 35-45% mais do que 4 camadas

- 8 camadas:50-60% mais do que 6 camadas

- 12 camadas+: Impacto significativo no rendimento

Aplicações de vanguarda

- Estações de base 5G: conjuntos de antenas mmWave

- Aceleradores de IA: Interconexões de memória HBM

- Condução autónoma:Controladores de domínio

Árvore de decisão de seleção de camadas de PCB

3 passos para determinar as camadas ideais da sua placa de circuito impresso:”

- Análise de sinais

- Contagem de sinais a alta velocidade (>100MHz)

- Densidade diferencial de pares (pares/cm²)

- Requisitos especiais de impedância (por exemplo, 90Ω USB)

2. Avaliação da potência

- Contagem do domínio da tensão

- Necessidades máximas de corrente (A/mm)

- Percentagem de circuito sensível ao ruído

3. Compensações de custos

- Restrições orçamentais ($/cm²)

- Volume de produção (K unidades/mês)

- Tolerância ao risco de iteração

A maior parte da eletrónica moderna equilibra de forma óptima o desempenho/custo com 4-6 camadas!

Cinco regras de ouro para a conceção de camadas de PCB

- Regra 3:1: 1 plano de terra por cada 3 camadas de sinal

Exceção: Os circuitos de RF precisam de uma referência 1:1 - Princípio 20H: Plano de potência inserido 20× espessura dieléctrica

Abordagem moderna: Utilizar anéis de proteção dos bordos - Lei da Simetria: Evitar a deformação (distribuição equilibrada do cobre)

Parâmetro-chave: ΔCu<15% nas camadas - Sem divisão cruzada: Nunca encaminhar a alta velocidade por cima de divisões de aviões

SoluçãoUtilizar condensadores de costura - Fórmula de otimização de custos:

Camadas ideais = ceil(Necessidades totais de encaminhamento / Eficiência das camadas)Valores da experiência: 4 camadas ≈55%, 6 camadas ≈70% de utilização

Consulte-nos para obter os melhores conselhos

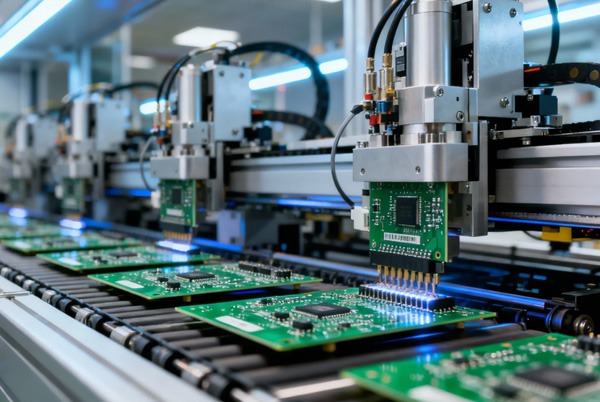

Tecnologia de camadas de PCB

1. Integração heterogénea

- PCBs de componentes incorporados (EDC)

- Integração 2,5D de interpositores de silício

- Estruturas multicamadas impressas em 3D

2.Inovações de materiais

- Substratos de perdas ultra-baixas (Dk<3.0)

- Dieléctricos térmicos (5W/mK+)

- Materiais laminados recicláveis

3.Revolução do design

- Otimização de camadas com base em IA

- Pilhas de computação quântica

- Arquitecturas de encaminhamento neuromórficas

Previsão do sector: Até 2026, as placas de circuito impresso com mais de 20 camadas ocuparão 35% dos mercados de topo de gama, mas as placas com 4-8 camadas continuarão a ser as principais (>60%)

Perguntas mais frequentes

Q: Quando é que devo aumentar as camadas de PCB?

R: Considerar mais camadas quando:

- >30% das redes exigem longos desvios

- O ruído de potência provoca instabilidade

- Os testes EMC falham repetidamente

P: Os desenhos de 4 camadas podem substituir os de 6 camadas?

R: Possível com:

Microvias HDI

2 planos de sinal + 2 planos mistos

Capacitância enterrada

Mas sacrifica ~20% de margem de desempenho

P: Prazo de entrega típico para PCB multicamadas?

R: Entrega normal:

- 4 camadas: 5-7 dias

- 6 camadas:7-10 dias

- 8 camadas+: 10-14 dias

(Serviços expeditos reduzidos em 30-50%)

Seleção razoável do número de camadas de PCB

- Necessidades de desempenho > Especificações teóricas: Os testes reais superam as simulações

- Controlo de custos requer uma análise do ciclo de vida: Incluir riscos de retrabalho

- Cadeia de fornecimento alinhamento: Evitar o excesso de engenharia

"A melhor escolha de camadas de PCB satisfaz as necessidades actuais, permitindo futuras actualizações!";

Publicações relacionadas