Conceção de layout de PCB de alta velocidade

Índice

O papel do design de roteamento de PCB de alta velocidade

O encaminhamento adequado assegura a integridade do sinal, melhora a compatibilidade electromagnética (CEM) e aumenta a fiabilidade do sistema.

1. Garantir a integridade do sinal

Uma estratégia de encaminhamento bem concebida pode minimizar a reflexão do sinal e a diafonia, garantindo a transmissão estável de dados de alta velocidade (como USB 3.0, HDMI, etc.) na placa de circuito impresso.

2. Compatibilidade electromagnética

Ao adotar um sistema de grelha razoável para normalizar os canais de encaminhamento, os conflitos de espaçamento entre componentes podem ser reduzidos; a sinalização diferencial, as camadas de blindagem e os planos de terra de alimentação podem minimizar a interferência electromagnética (EMI).

3. Fiabilidade do sistema

Ao controlar a densidade do encaminhamento e a utilização de recursos, os caminhos redundantes podem ser minimizados e os custos reduzidos; as vias cegas e as vias enterradas podem otimizar o encaminhamento de alta densidade. Os layouts de grade padronizados podem evitar riscos de curto-circuito.

Fundamentos da conceção de PCB de alta velocidade

1. Elementos-chave da integridade do sinal (SI)

- Efeitos da linha de transmissão: Os sinais de alta frequência requerem a consideração da teoria das linhas de transmissão para controlar a correspondência da impedância caraterística

- Supressão do reflexo: Utilizar resistências de terminação para reduzir a reflexão do sinal

- Controlo de diafonia: Aplicar a regra dos 3W para minimizar a diafonia próxima (NEXT) e a diafonia distante (FEXT)

2. Noções básicas de integridade de potência (PI)

- Rede de distribuição de energia (PDN): Otimizar a conceção do plano de terra de potência

- Condensadores de desacoplamento: Implementar redes de desacoplamento com combinações de "10μF+0,1μF+0,01μF

- Ruído de comutação simultâneo (SSN): Reduzir o impacto da saída de comutação simultânea (SSO) através de uma disposição adequada

Alta velocidade Design de empilhamento de PCB

1. Estrutura de empilhamento de placas multicamadas

- Empilhamento típico: Configuração recomendada de 8 camadas (superior-Sig-Sig-Pwr-Sig-Gnd-Sig-bottom)

- Controlo da impedância: Atingir 50Ω de impedância simples e 100Ω de impedância diferencial através de um design empilhado

- Materiais dieléctricos: Selecionar materiais para placas de alta frequência com baixa constante dieléctrica (Dk) e baixo fator de dissipação (Df)

2. Aplicação avançada da regra 20H

- Recuo do plano de potência: O plano de potência deve recuar 20H em relação ao plano de terra

- Supressão de EMI: Reduz eficazmente a radiação dos bordos em 30-40dB

- Dispositivos móveis: Adicionar anéis de proteção e vias de costura

Técnicas de encaminhamento de sinais de alta velocidade

1. Encaminhamento de sinalização diferencial

- Comprimento correspondente: Controlo da correspondência do comprimento do par diferencial com ±5mil

- Correspondência de fases: Manter a diferença de fase entre sinais positivos/negativos <5ps

- Atraso intra-par: Controlo rigoroso da inclinação intra-pares

2. Tratamento especial dos sinais de relógio

- Guardar vestígios: Colocar traços de proteção de terra em ambos os lados das linhas de relógio

- Técnicas de terminação: Utilizar terminação de origem ou terminação de fim

- Controlo de jitter: Reduzir os desvios de temporização através de redes de distribuição de relógios com desvios reduzidos

Otimização da integridade da energia

1. Conceção da rede de distribuição de energia (PDN)

- Impedância alvo: Manter a impedância PDN abaixo do valor-alvo em todas as frequências

- Capacitância plana: Utilizar a capacitância nativa entre os planos de alimentação e terra

- Cobertura de frequências: A rede de desacoplamento deve cobrir a gama de DC a GHz

2. Supressão do ruído de comutação simultâneo (SSN)

- Segmentação de potência: Segmentar corretamente os diferentes domínios de tensão

- Caminho de regresso: Assegurar que os sinais de alta velocidade têm caminhos de retorno de baixa impedância

- Através da colocação: Vias de alimentação suficientes para reduzir a indutância do circuito

Conceção EMC/EMI

1. Conceção da compatibilidade electromagnética (CEM)

- Controlo das radiações: Reduzir as emissões por radiação através da regra 20H e dos traços de proteção

- Circuitos sensíveis: Implementar blindagem para circuitos sensíveis à RF

- Conceção do filtro: Instalar filtros do tipo π ou do tipo T nas interfaces de E/S

2. Otimização do sistema terrestre

- Ligação à terra híbrida: Implementar uma estratégia de ligação à terra híbrida para circuitos digitais/analógicos

- Controlo da segmentação: Evitar o ressalto do solo causado por uma segmentação incorrecta da placa de terra

- Ligação à terra multiponto: Utilizar uma ligação à terra multiponto para os circuitos de alta frequência

Verificação de design de PCB de alta velocidade

1. Análise da integridade do sinal (SI)

- Análise no domínio do tempo: Avaliar a qualidade do sinal através de diagramas oculares

- Análise no domínio da frequência: Analisar as caraterísticas de transmissão utilizando parâmetros S

- Verificação da simulação: Efetuar simulações de pré-layout e pós-layout com HyperLynx ou ADS

2. Verificação da integridade da alimentação (PI)

- Teste de impedância: Realizar testes de impedância PDN do VRM ao chip

- Medição do ruído: Medir a ondulação de potência e o ruído

- Análise térmica: Avaliar a subida de temperatura de traços de alta corrente

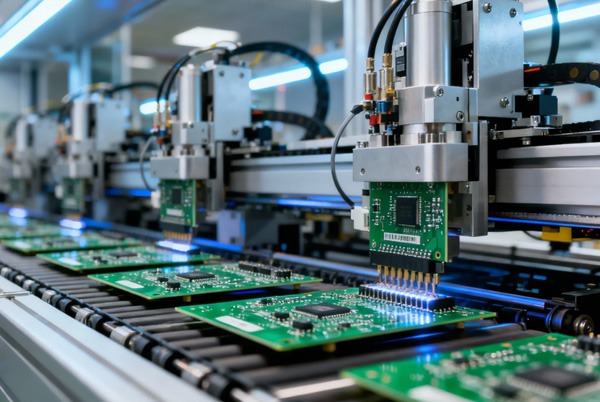

Processo de fabrico

1. Conceção para fabrico (DFM)

- Controlo da largura do traço: Considerar os efeitos do fator de corrosão

- Rácio de aspeto: Manter a relação entre a espessura da placa e o diâmetro do furo <8:1

- Acabamento da superfície: Preferir acabamentos de superfície ENIG ou prata de imersão

2. Seleção de materiais

Ao aplicar estes princípios de conceção da disposição de PCB de alta velocidade e técnicas de otimização de palavras-chave, a integridade do sinal, a integridade da potência e o desempenho EMC das PCB de alta velocidade podem ser significativamente melhorados. Durante o processo de conceção, deve ser dada especial atenção a factores-chave como o controlo da impedância, a redução das diafonias e a otimização da integridade da potência, utilizando simultaneamente métodos de simulação e medição para verificação.

Principais considerações para o design de roteamento de PCB de alta velocidade

Controlo da impedância e seleção da linha de transmissão

O controlo da impedância é fundamental para PCB de alta velocidade desenho. Selecione a estrutura de linha de transmissão apropriada (por exemplo, microstrip ou stripline) com base na frequência do sinal, na espessura da placa e na constante dielétrica. Use ferramentas de cálculo de impedância (como o Polar SI9000 ou a calculadora integrada do Altium Designer) para determinar com precisão a impedância do traço e garantir que ela atenda aos requisitos do projeto. Por exemplo, pares diferenciais normalmente exigem impedância de 90Ω ou 100Ω, necessitando de um controle rigoroso sobre a largura e o espaçamento do traço. Evite descontinuidades de impedância causadas por curvas em ângulo reto, vias, ramificações ou alterações súbitas na largura do traço, uma vez que estas podem levar a reflexões de sinal e integridade degradada.

Estratégias de encaminhamento para reduzir a diafonia

A diafonia é uma grande ameaça à integridade do sinal de alta velocidade. Para minimizar o seu impacto:

- Aumentar o espaçamento entre traços: Siga a regra 3W (espaçamento entre traços adjacentes ≥ 3× largura do traço) para reduzir o acoplamento eletromagnético.

- Utilizar sinalização diferencial: Os pares diferenciais (por exemplo, USB, PCIe, LVDS) suprimem eficazmente o ruído de modo comum, mas exigem uma largura e um espaçamento precisos dos traços de correspondência de impedância, bem como uma correspondência rigorosa do comprimento.

- Adicionar camadas de proteção: Coloque planos de terra (GND) à volta de sinais sensíveis (por exemplo, linhas de relógio, sinais de RF) para isolar interferências externas.

- Evitar traços paralelos longos: O encaminhamento paralelo aumenta o acoplamento - opte por cruzamentos ortogonais ou por um maior espaçamento.

Reduzir as reflexões e otimizar a integridade do sinal

As reflexões de sinal podem causar sobreposição, anelamento e outros problemas de estabilidade. Os métodos de otimização incluem:

- Controlo do comprimento do traço: Sinais de alta velocidade (por exemplo, DDR, HDMI) requerem uma correspondência rigorosa de comprimento para evitar desvios de tempo devido a atrasos de propagação.

- Correspondência de impedância com resistências de terminação: Escolha o método de terminação apropriado (série, paralelo ou terminação Thevenin) com base nas caraterísticas da linha de transmissão para eliminar reflexões.

- Otimização dos planos de potência e de terra: Utilize camadas de potência de baixa impedância e planos de terra sólidos, juntamente com condensadores de desacoplamento estrategicamente colocados (por exemplo, combinações de 0,1 μF e 10 μF), para reduzir o ruído de potência.

Conceção final e verificação

Depois de completar o encaminhamento, efetuar uma verificação das regras de conceção (DRC) para garantir a conformidade com os requisitos de fabrico de PCB. Utilizar ferramentas de simulação SI/PI (Integridade de Sinal/Integridade de Potência) (por exemplo, HyperLynx ou ADS) para validar trajectórias de sinais críticos e identificar antecipadamente potenciais problemas.

Ao implementar estas medidas, a qualidade do sinal em PCB de alta velocidade pode ser significativamente melhorada, garantindo a estabilidade e a fiabilidade do sistema.

Recomendações relacionadas

Guia de conceção e esquematização de PCB de alta frequência

Publicações relacionadas