Problemi comuni nel miglioramento dell'affidabilità dei PCB

Indice per materie

Come calcolare l'impedenza dei circuiti stampati?

Il calcolo dell'impedenza del PCB garantisce l'integrità del segnale, soprattutto per i circuiti ad alta velocità e RF.

1. Determinazione dell'impilamento e della geometria del PCB

- Conteggio degli strati: Singolo, doppio o multistrato.

- Larghezza della traccia (W) nonché spessore (T): Critico per il controllo dell'impedenza.

- Spessore del dielettrico (H): Distanza tra il livello del segnale e il piano di riferimento (ad esempio, la terra).

- Peso del rame: In genere da 0,5 oz (17,5 µm) a 2 oz (70 µm).

2. Identificare la costante dielettrica (Dk o εᵣ)

- FR-4: ~4,3-4,8 (varia con la frequenza).

- Rogers RO4003C: ~3,38 (bassa perdita per RF).

- Poliammide: ~3,5 (PCB flessibili).

- Nota: Dk diminuisce leggermente alle frequenze più alte.

3. Scegliere il metodo di calcolo dell'impedenza

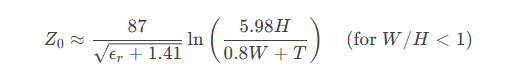

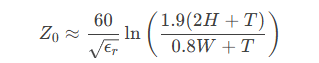

Microstriscia (traccia dello strato esterno sul piano di massa):

Stripline (strato interno tra due piani di massa):

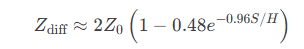

Coppia differenziale: Richiede la spaziatura (S) tra le tracce.

4. Utilizzare calcolatori o strumenti per l'impedenza

- Strumenti online: Saturn PCB Toolkit, EEWeb Calculator.

- Software PCB: Altium Designer, KiCad o Cadence includono calcolatori di impedenza integrati.

- Simulatori EM: Ansys HFSS, CST (per progetti avanzati).

5. Ottimizzare il progetto in base ai risultati

- Regolare larghezza della traccia (larghezza ↑ → impedenza ↓).

- Modificare spessore del dielettrico (↑ H → ↑ impedenza).

- Modifica spaziatura tra le tracce per le coppie differenziali.

- Selezionare materiali con Dk appropriato (ad esempio, Rogers per RF).

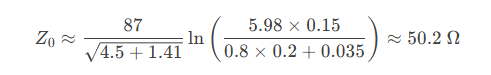

Esempio di calcolo (FR-4 Microstrip)

Dato:

- Larghezza della traccia (W) = 0,2 mm

- Spessore del dielettrico (H) = 0,15 mm

- Spessore del rame (T) = 0,035 mm

- εᵣ = 4,5

Utilizzando la formula della microstriscia:

Corrisponde all'impedenza standard di 50Ω per i segnali RF.

Come considerare l'integrità del segnale in Progettazione PCB?

1. Progettazione del layout

Nella progettazione del layout dei circuiti stampati, è importante considerare la disposizione delle linee di segnale, delle linee di alimentazione e delle linee di terra ed evitare le interferenze causate dall'incrocio di linee di segnale, linee di alimentazione e linee di terra. Inoltre, è essenziale ridurre al minimo la lunghezza delle linee di segnale per ridurre la diafonia e il ritardo.

2. Corrispondenza di impedenza

Quando si progettano linee di segnale ad alta velocità, è necessario eseguire l'adattamento di impedenza per garantire che l'impedenza delle linee di segnale corrisponda all'impedenza della sorgente e del carico del segnale, evitando così la riflessione e la diafonia del segnale.

3. Instradamento delle linee di segnale

Nella progettazione dei circuiti stampati, anche l'instradamento delle linee di segnale influisce sull'integrità del segnale e deve seguire determinate regole. Ad esempio, le linee di segnale differenziali devono mantenere una certa spaziatura ed essere instradate in parallelo, mentre le linee di segnale single-ended devono essere instradate parallelamente alle linee di terra e le curve delle linee di segnale devono essere ridotte al minimo.

4. Alimentazione e messa a terra

Nella progettazione dei PCB, anche la progettazione dell'alimentazione e della messa a terra influisce sull'integrità del segnale. È necessario utilizzare un'alimentazione e una messa a terra stabili e ridurre al minimo la resistenza e l'induttanza dell'alimentazione e della messa a terra.

5. Verifica della simulazione

Una volta completata la progettazione del PCB, è necessaria una verifica di simulazione per garantire che l'integrità del segnale soddisfi i requisiti. Grazie alla simulazione, è possibile individuare problemi quali il ritardo del segnale, la riflessione e la diafonia e ottimizzare il progetto del PCB.

Come considerare la compatibilità elettromagnetica (EMC) nella progettazione dei PCB?

1. Layout del PCB per la compatibilità elettromagnetica

- Ridurre al minimo l'instradamento parallelo: Evitare lunghi percorsi paralleli tra le tracce di segnale e quelle di alimentazione/terra per ridurre la diafonia e l'accoppiamento elettromagnetico.

- Isolamento dei segnali critici: Separare i segnali analogici sensibili e ad alta velocità (ad esempio, orologi, RF) dai circuiti rumorosi (ad esempio, alimentatori a commutazione).

- Strategia di impilamento dei livelli:

- Utilizzare piani di massa solidi adiacenti ai livelli di segnale per fornire una schermatura.

- Instradare i segnali ad alta velocità sugli strati interni tra i piani di massa per il contenimento.

2. Tecniche di messa a terra

- Piani di massa a bassa impedenza: Utilizzare piani di massa ininterrotti per minimizzare i loop di massa e ridurre le emissioni irradiate.

- Dividere con cura i terreni: Separare le masse analogiche/digitali solo se necessario, con un unico punto di connessione (ad esempio, perlina di ferrite o resistenza da 0Ω).

- Via Cuciture: Collocare più vias di terra intorno alle tracce ad alta frequenza o ai bordi della scheda per sopprimere le risonanze della cavità.

3. Filtraggio e soppressione

- Perline di ferrite: Da aggiungere alle linee di alimentazione/IO per bloccare i disturbi ad alta frequenza.

- Condensatori di disaccoppiamento: Posizionare vicino ai pin di alimentazione del circuito integrato (ad esempio, 0,1μF + 1μF) per filtrare i disturbi ad alta e media frequenza.

- Induttanze di modo comune: Utilizzare su coppie differenziali (ad esempio, USB, Ethernet) per sopprimere la radiazione di modo comune.

4. Schermatura e progettazione dell'interfaccia

- Schermatura dei cavi: Utilizzare connettori schermati (ad esempio, USB, HDMI) con messa a terra a 360° rispetto allo chassis.

- Schermatura a livello di scheda: Aggiungere barattoli di metallo o rivestimenti conduttivi sui circuiti RF sensibili.

- Protezione dei bordi: Disporre le tracce sensibili lontano dai bordi della scheda; utilizzare tracce di protezione o una colata di rame con messa a terra intorno ad esse.

5. Simulazione e test

- Analisi pre-layout: Utilizzare strumenti come ANSYS HFSS o CST per modellare i punti caldi di radiazione.

- Verifica successiva al layout:

- Eseguire scansioni in campo vicino per identificare le fonti di emissione.

- Esecuzione di test di conformità (ad esempio, FCC, CE) per le emissioni irradiate/condotte.

- Iterazione del progetto: Ottimizzare in base ai risultati dei test (ad esempio, aggiungendo resistenze di terminazione o regolando la spaziatura delle tracce).

Esempi di correzioni:

- Un orologio da 100 MHz irradia eccessivamente: Aggiungere resistenze di terminazione in serie o instradare tra piani di massa.

- Rumore di commutazione dell'alimentazione: implementare filtri π (LC) all'ingresso/uscita.

Integrando queste pratiche, i PCB possono soddisfare gli standard EMC (ad esempio, IEC 61000) riducendo al minimo le costose riprogettazioni. Prototipare e testare sempre in anticipo!

Come considerare l'integrità di potenza (PI) nella progettazione di PCB?

1. Layout della traccia di alimentazione

- Tracce corte e larghe: Ridurre al minimo la resistenza (R) e l'induttanza parassita (L) per ridurre la caduta di tensione e il rumore.

- Evitare l'instradamento parallelo con le tracce del segnale: Impediscono che il rumore di alimentazione si inserisca nei segnali sensibili (ad esempio, orologi, circuiti analogici).

- Strategia a strati:

- Nelle schede multistrato, dedicare interi strati ai piani di alimentazione e di terra.

- I rail di alimentazione critici (ad esempio, la tensione del core della CPU) devono avere piani di alimentazione dedicati.

2. Filtraggio di potenza

- Condensatori di disaccoppiamento:

- Condensatori elettrolitici di massa (10-100μF) agli ingressi di alimentazione per stabilizzare la tensione.

- Piccoli condensatori ceramici (0,1μF) vicino ai pin del circuito integrato per filtrare i disturbi ad alta frequenza.

- Filtri LC:

- Aggiungere filtri π (condensatore + induttore) per i moduli sensibili al rumore (ad esempio, i PLL).

3. Alimentazione e messa a terra

- Percorsi di ritorno a bassa impedenza:

- Utilizzate piani di massa solidi; evitate gli sdoppiamenti che causano discontinuità di impedenza.

- Più vias per collegare i piani di alimentazione e di terra (riduce l'induttanza dei vias).

- Messa a terra a stella:

- Circuiti sensibili e ad alta potenza separati, con messa a terra in un unico punto.

4. Simulazione e convalida

- Analisi della rete PDN (Power Delivery Network):

- Impedenza del bersaglio: ( Z_{{testo{target}} = \frac{\Delta V}{\Delta I} ).

- Strumenti: ANSYS SIwave, Cadence Sigrity.

- Test di ondulazione e rumore:

- Verificare i livelli di rumore di potenza con oscilloscopi o simulazioni.

Come incorporare il Design for Testability (DFT) nella progettazione dei PCB?

1. Punti di prova e interfacce

- Punti di test del segnale critico:

- Prevedere vias o pad (diametro ≥1 mm, distanza ≥2,54 mm) per l'accesso alla sonda.

- Etichettare i punti di test (ad esempio, TP1, TP2).

- Interfacce standard:

- Posizionare le interfacce JTAG, UART o SWD vicino ai bordi della scheda.

2. Etichettatura della scheda (serigrafia)

- Marcature dei componenti:

- Etichettare i designatori di riferimento (ad esempio, R1, C2), la polarità (+/-) e il pin 1.

- Utilizzare una serigrafia ad alto contrasto (bianco/nero).

- Zone funzionali:

- Delineare le aree (ad esempio, "Sezione alimentazione") per facilitarne l'identificazione.

3. Tecniche di test programmabili

- Scansione perimetrale (JTAG):

- I circuiti integrati conformi allo standard IEEE 1149.1 (ad esempio, FPGA, MCU) consentono di eseguire test di interconnessione.

- Apparecchiature di test automatizzate (ATE):

- Interfacce di riserva del dispositivo di prova (ad esempio, pad per pin pogo).

4. Simulazione e convalida

- Controlli delle regole DFT:

- Garantire la copertura dei punti di test (ad esempio, >90% di reti accessibili).

- Analisi delle modalità di guasto:

- Convalida dei circuiti di prova mediante simulazioni SPICE.

Principi di progettazione chiave a confronto

| Integrità di potenza (PI) | Progettazione per la testabilità (DFT) |

|---|---|

| Distribuzione di potenza a bassa impedenza | Accessibilità fisica del punto di prova |

| Ottimizzazione del condensatore di disaccoppiamento | Supporto JTAG/scansione limite |

| Ridurre al minimo l'accoppiamento potenza-segnale | Etichettatura chiara dei componenti e delle interfacce |

| Simulazione PDN e analisi del ripple | Design compatibile con ATE |

Esempi:

- Ottimizzazione PI: Piani di alimentazione della memoria DDR4 con più condensatori 0805 da 0,1μF (impedenza target ≤0,1Ω).

- Implementazione DFT: Scheda di controllo industriale con 20 punti di prova per il test automatico delle sonde volanti.

Affrontando sistematicamente PI e DFT, i progettisti possono migliorare le prestazioni di potenza, l'efficienza dei test e l'affidabilità della produzione.

Messaggi correlati