Beim digitalen Hochgeschwindigkeits-Leiterplattendesign ist die Kontrolle der Leiterbahnimpedanz ein entscheidender Faktor zur Gewährleistung der Signalintegrität. Als Profi PCB-HerstellerTOPFAST weiß, dass die präzise Anpassung der äußeren Kupferdicke und der Leiterbahngeometrie für das Erreichen von Frequenzen im GHz-Bereich und Datenraten von mehr als 10 Gbit/s entscheidend ist. Dieser Artikel analysiert den Korrelationsmechanismus zwischen Kupferdicke und Impedanz aus technischer Sicht und bietet umsetzbare Designrichtlinien, die Ingenieuren helfen, eine stabile und zuverlässige Leistung in Hochgeschwindigkeitsübertragungssystemen zu erreichen.

Inhaltsübersicht

Warum müssen wir uns auf die Leiterbahnimpedanz konzentrieren?

Die Kontrolle der Leiterbahnimpedanz ist die physikalische Grundlage der Digitales Hochgeschwindigkeits-Leiterplatten-Design. Impedanzfehlanpassungen können Signalreflexionen, Klingeln und Timing-Jitter verursachen, was zu erhöhten Bitfehlerraten führt. Insbesondere in Frequenzbändern über 5 GHz kann selbst eine Impedanzabweichung von ±5% das Schließen des Augendiagramms um mehr als 40% verschlechtern. Praktische Fälle zeigen, dass Hochgeschwindigkeitsbusse, wie DDR5-Speicherschnittstellen und PCIe 5.0, eine Impedanzkonsistenz von ±3% erfordern.

Was ist das Wesen der Spurenimpedanz?

Die Leiterbahnimpedanz ist im Wesentlichen die Wellenimpedanz, die sich ergibt, wenn sich elektromagnetische Wellen durch eine Übertragungsleitungsstruktur ausbreiten, und wird durch verteilte Induktivität und Kapazität bestimmt. Für digitale Hochgeschwindigkeitsschaltungen sind die üblicherweise verwendeten 50Ω-Single-Ended-Impedanz- und 100Ω-Differenzialimpedanz-Standards keine willkürliche Wahl, sondern optimale Lösungen, die einen Ausgleich zwischen Leistungsübertragungseffizienz, Signaldämpfung und Rauschtoleranz schaffen.

Branchendaten zeigen, dass Signalintegritätsprobleme aufgrund von Impedanzfehlern bis zu 34% aller Probleme ausmachen. Bei einer SerDes-Schnittstelle mit 28 Gbit/s kam es beispielsweise zu einer Impedanzschwankung von 8% aufgrund einer Abweichung von 2 μm bei der äußeren Kupferdicke, was letztlich zu einer Verschlechterung der Bitfehlerrate von 10-¹² auf 10-⁸ führte. Dies verdeutlicht die entscheidende Rolle einer präzisen Impedanzkontrolle in Hochgeschwindigkeitssystemen.

Wie wirkt sich die Kupferdicke auf die Impedanz aus?

Quantitative Beziehung zwischen Dicke und Impedanz

Die Kupferdicke bei der Leiterplattenherstellung wird in der Regel in Unzen pro Quadratfuß (1 oz/ft² ≈ 35μm) gemessen. Die Auswahl der Außenkupferdicke erfordert ein Gleichgewicht zwischen Strombelastbarkeit, Hochfrequenzverlust und Impedanzgenauigkeit. Gemessene Daten zeigen:

- 0,5 oz (17,5μm) Kupferdicke: Geeignet für Ultra-High-Speed-Signale (>25 Gbps), ermöglicht 3 mil feine Leiterbahnbreiten, jedoch mit höherem Gleichstromwiderstand.

- 1 oz (35μm) Kupferdicke: Eine ausgewogene Wahl, die 5-8 mil Leiterbahnbreiten unterstützt, um eine Impedanzkontrolle von 50±2Ω zu erreichen.

- 2 oz (70μm) Kupferdicke: Geeignet für Leistungspfade, aber mit einer Skin-Tiefe von nur 0,66μm bei 10 GHz, was zu einer geringen effektiven Nutzung führt.

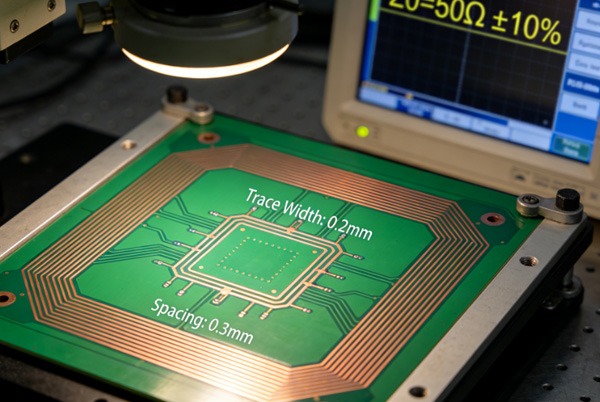

Unter Verwendung von Impedanzberechnungsmodellen, mit einer dielektrischen Dicke von 5 mil und Er=4,2:

- 1 Unze Kupferstärke: 8,2 mil Leiterbahnbreite ergibt 50Ω Impedanz.

- 0,5 oz Kupferdicke: 6,8 mil Leiterbahnbreite ergibt die gleiche Impedanz.

- 2 Unzen Kupferstärke: Erfordert eine Leiterbahnbreite von 11,5 mil, um 50Ω zu erreichen.

Praktische Herausforderungen im Herstellungsprozess

Galvanisierungs-, Verdickungs- und Ätzunterschneidungseffekte während der Leiterplattenherstellung können dazu führen, dass die endgültige Kupferdicke von den Entwurfsspezifikationen abweicht. Statistiken zeigen, dass eine Standard-1-oz-Kupferschicht nach der Galvanisierung zwischen 1,2-1,8 mil (30-45μm) variieren kann, was zu Impedanzschwankungen von bis zu ±6% führt.

Die Bewältigung dieser Herausforderung erfordert umfassende Maßnahmen:

- Implementierung von Echtzeit-Galvaniküberwachungssystemen zur Kontrolle von Kupferdickenabweichungen.

- Stellen Sie die Kompensationswerte für die Leiterbahnbreite auf der Grundlage des Ätzfaktors ein.

- Selektive galvanische Beschichtung von Hochgeschwindigkeitssignalschichten.

Vier wichtige Konstruktionsprinzipien: Die Grundlage einer präzisen Impedanzkontrolle von Leiterbahnen

1. Optimierung der Leiterbahngeometrie anhand der Zielimpedanz

Empfohlene Gestaltungsrichtlinien:

- Einseitige 50Ω-Leiterbahnen: Wenn die dielektrische Dicke H ≈ 5-6 mil beträgt, ist die Leiterbahnbreite W ≈ 2,1 × H (bei 1 oz Kupferdicke).

- Differential 100Ω Paare: Optimaler Kopplungskoeffizient, wenn der Leiterbahnabstand S ≈ 1,5 × Leiterbahnbreite.

- Kantengekoppelt vs. Breitseitengekoppelt: Unterhalb von 10 GHz ist die Kantenkopplung vorzuziehen, da sie die Kontrolle der Impedanzkonsistenz erleichtert.

2. Technische Überlegungen zum Management dielektrischer Schichten

Die Dielektrizitätskonstante (Dk) und die Gleichmäßigkeit der dielektrischen Dicke wirken sich direkt auf die Impedanzstabilität aus. Empfohlene Ansätze:

- Verwenden Sie verlustarme Materialien (z. B. MEGTRON6, Dk=3,2) anstelle von FR-4 (Dk=4,2-4,5).

- Verwendung symmetrischer Prepreg-Strukturen zur Vermeidung von Laminierverzug.

- Reserve von ±10% für dielektrische Dickenanpassung in Stack-up-Designs.

3. Proaktive Strategien für den Umgang mit Kupferdickenschwankungen

Ein dreiphasiges Kontrollverfahren sorgt für Konsistenz:

- Entwurfsphase: Simulieren Sie auf der Grundlage der endgültigen galvanischen Dicke und nicht der Nenndicke.

- Herstellungsphase: Implementierung einer Echtzeit-Impedanz-Coupon-Überwachung mit ≥3 Testpunkten pro Platte.

- Validierungsphase: Erreichen einer TDR-Stichprobenabdeckung von nicht weniger als 20%.

4. Systematische Methoden der Materialauswahl

Wählen Sie Materialkombinationen auf der Grundlage der Frequenzanforderungen:

- <5 GHz: Standard FR-4 Materialien.

- 5-20 GHz: Materialien mit mittleren Verlusten (z. B. TU-768).

- >20 GHz: Ultra-low-loss Materialien (z.B. RO3003).

Praktische Lösungen zur Bewältigung von Herausforderungen bei der Signalintegrität

Unterdrückung von Impedanzfehlanpassungsreflexionen

Wenn ein Signal auf eine Impedanzdiskontinuität trifft, ist der Reflexionskoeffizient ρ = (Z₂ - Z₁) / (Z₂ + Z₁). Die technische Praxis zeigt:

- Verjüngte Leiterbahnbreiten können Reflexionen von 5%-Impedanzübergängen auf unter -35 dB reduzieren.

- Die Aushöhlung der Referenzschicht in den Bereichen der Steckverbinderpads kompensiert die Auswirkungen der kapazitiven Belastung.

Wirksame Maßnahmen zur Kontrolle des Übersprechens

Mit zunehmender Kupferdicke verstärkt sich die elektromagnetische Kopplung. Empfohlene Maßnahmen:

- 3W-Regel: Ein Leiterbahnabstand ≥ 3 mal die Leiterbahnbreite reduziert das Übersprechen in der Ferne um 15 dB.

- Erden Sie Durchkontaktierungen: Platzieren Sie Abschirmungsvias alle 50 mil zwischen differentiellen Paaren.

- Ungleichmäßige Dielektrika: Verwenden Sie Materialien mit hohem Dk-Wert zwischen benachbarten Signalschichten, um die Isolierung zu erhöhen.

Ausgleich von Hochfrequenzverlusten

Bei der Wahl der Kupferdicke muss ein Kompromiss zwischen Leitungsverlust und dielektrischem Verlust gefunden werden:

- Unterhalb von 10 GHz: Der Leitungsverlust dominiert, so dass eine größere Kupferdicke von Vorteil ist.

- Über 10 GHz: Der Skin-Effekt wird signifikant, wobei die Rauheit der Kupferoberfläche kritischer ist als die Dicke.

- Tatsächliche Daten: Die Verwendung von VLP-Kupfer (Very Low Profile) kann die Einfügedämpfung bei 10 GHz um 20% reduzieren.

Fünf praktische Techniken: Vollständige Kontrolle vom Entwurf bis zur Fertigung

- Multi-Physik-Co-Simulation implementieren

Kombinieren Sie die Simulation des elektromagnetischen Feldes mit der Prozesssimulation, um die Auswirkungen von Fertigungsabweichungen auf die Impedanz vorherzusagen und das Design proaktiv zu optimieren. - Statistische Prozesskontrollsysteme einrichten

Erstellen Sie Dk/Df-Datenbanken für jede Materialcharge und passen Sie Prozessparameter in Echtzeit an, um Impedanzkonsistenz zu gewährleisten. - Intelligente Anwendung von TDR-Tests

Verwenden Sie die Zeitbereichsreflektometrie zur Erstellung von Impedanzverteilungskarten, um lokale Anomalien zu identifizieren, anstatt sich nur auf Durchschnittswerte zu konzentrieren. - Digitaler Übergabeprozess vom Entwurf bis zur Fertigung

Verwendung intelligenter Datenformate zur direkten Übertragung von Impedanzanforderungen und Kupferdickentoleranzen an die Produktionsanlagen. - Frühzeitige Einbindung in die Produktion

Bitten Sie Experten aus der Fertigung bereits in der Anfangsphase um Teilnahme an der Entwurfsprüfung, um spätere kostspielige Änderungen zu vermeiden.

Wie TOPFAST eine präzise Steuerung für Hochgeschwindigkeitsübertragungen ermöglicht

Beim Design digitaler Hochgeschwindigkeits-Leiterplatten ist die präzise Kontrolle der Außenkupferdicke und der Leiterbahnimpedanz zu einer Schlüsseltechnologie geworden, die die Systemleistung bestimmt. Durch ein tiefes Verständnis der mikroskopischen Auswirkungen von Kupferdickenschwankungen auf die Impedanz und die Implementierung einer vollständigen Prozesskontrolle vom Design bis zur Fertigung können Ingenieure die Herausforderungen der Hochgeschwindigkeitsübertragung im GHz-Zeitalter meistern.

Als professioneller Partner mit jahrelanger Erfahrung in der Leiterplattenherstellung bietet TOPFAST nicht nur hochpräzise Impedanzkontrolllösungen, sondern schafft auch Mehrwert für die Kunden durch systematische Dienstleistungen:

- Professionelle Unterstützung bei der Designberatung: Bibliotheken mit Impedanzentwurfsregeln, die auf Tausenden von erfolgreichen Fällen basieren.

- Fähigkeiten zur schnellen Überprüfung von Prototypen24-Stunden-Prototyping mit umfassenden Impedanztestberichten.

- Sicherstellung der Konsistenz der Chargenproduktion: Vollautomatische optische Prüfsysteme + Online-Impedanzüberwachung.

- Kontinuierliche technische Schulung und Austausch: Regelmäßige Seminare zum Hochgeschwindigkeits-Leiterplattendesign, in denen die neuesten praktischen Erfahrungen ausgetauscht werden.

Die Beherrschung der Kunst, Kupferdicke und Impedanz in Einklang zu bringen, erfordert nicht nur theoretisches Wissen, sondern auch umfangreiche praktische Erfahrungen. Wir empfehlen den Ingenieuren, bereits in den frühen Entwurfsphasen eng mit den Fertigungspartnern zusammenzuarbeiten und die Grundsätze des fertigungsgerechten Designs in den gesamten Prozess zu integrieren. Ganz gleich, ob es um die Herausforderungen von 112G PAM4-Systemen oder um die Schaffung der Hardware-Grundlage für Computerplattformen der nächsten Generation geht, eine präzise Impedanzkontrolle wird der Schlüssel zum Erfolg sein.

PCB-Impedanz FAQ

A: Impedanzfehlanpassungen können zu Signalreflexionen, Timing-Störungen und erhöhten Bitfehlerraten führen, insbesondere bei Frequenzen über 5 GHz, wo eine Abweichung von ±5% die Signalqualität um über 40% verschlechtern kann.

A: Eine größere Kupferdicke verringert den Widerstand pro Längeneinheit, verändert aber die Verteilung des elektromagnetischen Feldes und senkt die Impedanz. Beispielsweise erreicht eine Leiterbahnbreite von 8,2 mil bei 1 oz Kupfer 50Ω, während bei 2 oz Kupfer eine Verbreiterung auf 11,5 mil erforderlich ist, um die gleiche Impedanz zu erhalten.

A: Für eine einseitige 50-Ω-Leiterbahn mit einer dielektrischen Dicke von 5 mil und 1 oz Kupfer beträgt die Leiterbahnbreite etwa 8,2 mil. Genaue Berechnungen sollten mit Simulationswerkzeugen durchgeführt werden, die auf spezifischen dielektrischen Materialien basieren (z. B. FR-4 mit Dk ≈ 4,3).

A: Schwankungen der Kupferdicke nach der Beschichtung (üblicherweise ±15%)

Ätzunterschnitt führt zu Leiterbahnbreitenänderungen

Inkonsistente dielektrische Schichtdicke

Chargenschwankungen der Dielektrizitätskonstante (Dk) des Materials

A: Messung der Leiterbahnimpedanz mit TDR (Time Domain Reflectometry)

Empfohlener Stichprobentestumfang ≥20%

Überwachung des Prozesses mit Impedanz-Testcoupons

Datenvergleich durch gemeinsame Nutzung von Simulationsmodellen mit dem Hersteller