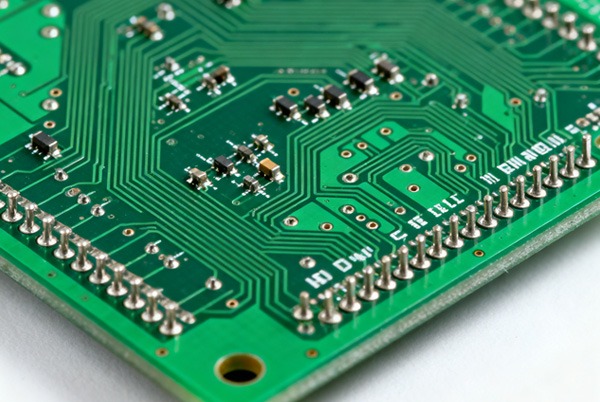

Este artículo profundiza en la compleja ingeniería de sistemas que interviene en los cálculos de separación de conductores para el diseño de placas de circuito impreso (PCB) de alta tensión. Más allá de las normas de seguridad básicas, se analiza la lógica subyacente del diseño del espaciado desde múltiples dimensiones, incluida la ciencia de los materiales, los mecanismos de fallo y la dinámica ambiental, proporcionando una orientación de futuro para el diseño de la fiabilidad de las PCB de alta tensión.

Tabla de contenidos

Diseño de la distancia entre conductores

El diseño de placas de circuito impreso de alta tensión ha evolucionado desde el mero cumplimiento de las normas a una compleja disciplina de ingeniería de sistemas que requiere un profundo conocimiento de distribución del campo eléctrico, comportamiento de la interfaz del material y efectos de acoplamiento ambiental. Cuando las tensiones de funcionamiento superan los 30 V CA / 60 V CC, el diseño de la separación entre conductores ya no es sólo una cuestión de "distancia de seguridad", sino que se convierte en un reto de optimización que implica acoplamiento multifísico.

1.1 La dualidad de los parámetros de espaciado

- Liquidación: El camino más corto a través del aire, regido principalmente por Ley de Paschenque presenta una compleja relación no lineal con la presión atmosférica, la humedad y la temperatura.

- Distancia de fuga: La trayectoria a lo largo de una superficie aislante, influida por fenómenos de interfaz tales como resistividad superficial, humectabilidad y acumulación de contaminación.

- Perspectiva clave: Para la misma distancia numérica, la fiabilidad de una vía de fuga suele ser inferior a la de un entrehierro, debido a la naturaleza variable en el tiempo de las condiciones de la superficie.

La perspectiva de la ciencia de los materiales

El Índice de Seguimiento Comparativo (ISC) suele simplificarse como una "etiqueta de grado" material, pero refleja fundamentalmente la estabilidad estructural de sustratos poliméricos sometidos a campos eléctricos.

2.1 El mecanismo microscópico del CTI

- Formación electroquímica de dendritas: Los ensayos CTI evalúan esencialmente la resistencia de un material a crecimiento electroquímico de cristales dendríticos.

- Efecto de acoplamiento térmico-eléctrico: Los materiales con alto CTI suelen presentar una mejor conductividad térmica y una temperatura de transición vítrea (Tg) más alta, lo que permite disipar más rápidamente los puntos calientes locales.

- Principio de correspondencia de materiales: Cuando CTI < 200, por cada descenso en el nivel de clasificación, la distancia de fuga requerida debe aumentar en 15-20%-una regla empírica no cuantificada explícitamente en las normas.

2.2 Desarrollo de sustratos avanzados

- Materiales compuestos de alta frecuencia y alta tensión: Materiales rellenos de PTFE/cerámica con CTI > 600, que combinan bajas pérdidas y alta resistencia al arco.

- Resinas epoxi nanomodificadas: Dopado con nanopartículas de SiO₂/Al₂O₃, mejora la resistencia mecánica al tiempo que aumenta el CTI en 30-50%.

Análisis en profundidad de los mecanismos de fallo

3.1 Modelo de acoplamiento multifactorial para el crecimiento del filamento anódico conductor (CAF)

Investigaciones recientes indican que la formación de CAF es el resultado de una interacción tripartita entre envejecimiento electroquímico, mecánico y térmico:

Tasa de crecimiento CAF = f(Intensidad del campo eléctrico) × g(Temperatura) × h(Humedad) × φ(Tensión mecánica)Donde la intensidad de campo eléctrico tiene un relación exponencialy por cada 10 °C de aumento de la temperatura, el riesgo de CAF se multiplica por 2-3.

3.2 Evolución dinámica de la contaminación superficial

El Grado de Contaminación no es un parámetro estático, sino un función del tiempo:

- Polvo + Humedad Efecto sinérgico: Cuando la humedad relativa > 60%, la resistividad del polvo ordinario puede descender en 3-4 órdenes de magnitud.

- Dinámica de la migración iónica: Bajo polarización de corriente continua, iones como Na⁺ y Cl- pueden migrar a velocidades de 0,1-1 μm/s, formando rápidamente canales conductores.

Marco de diseño jerárquico para sistemas de aislamiento de alta tensión

4.1 Aplicación técnica del sistema de aislamiento de cinco niveles

| Clase de aislamiento | Requisito básico | Espaciado Multiplicador | Escenario de aplicación |

|---|---|---|---|

| Aislamiento básico | Protección de fallo único | 1.0 | Dentro del equipo de Clase I |

| Aislamiento suplementario | Capa protectora redundante | 1.2-1.5 | Áreas críticas de seguridad |

| Doble aislamiento | Sistemas duales independientes | 1.8-2.0 | Equipos portátiles |

| Aislamiento reforzado | Una capa equivale a doble | 2.0-2.5 | Medicina/Aeroespacial |

| Aislamiento funcional | Sólo requisitos de rendimiento | 0.6-0.8 | Entre circuitos SELV |

4.2 El papel más profundo de los revestimientos conformados

- Efecto de homogeneización del campo eléctrico: Los revestimientos con una constante dieléctrica elevada (εᵣ > 4,5) pueden reducir el gradiente del campo eléctrico superficial en 30-40%.

- Resistividad volumétrica frente a resistividad superficial: Los revestimientos de parileno de alta calidad tienen una resistividad volumétrica > 10¹⁶ Ω-cm, pero la contaminación superficial aún puede crear vías de derivación.

- "Efecto amplificador" de los defectos de revestimiento: La intensidad del campo eléctrico en los defectos pinhole puede aumentar 10-100 vecesdesencadenando un colapso local.

Un modelo de corrección dinámica para calcular el espaciado

El método de tablas de consulta de las normas tiene limitaciones, por lo que es necesario introducir factores de corrección dinámica:

5.1 Base física de la corrección de altitud

Por cada 1000 m de altitud, la tensión de ruptura del aire disminuye aproximadamente 10%pero de forma no lineal:

Factor de corrección Kₐ = e^(h/8150) (donde h es la altitud en metros)En la práctica, a 2000 m de altitud, el espacio libre debe aumentar en 15-20%.

5.2 Consideración estadística de las sobretensiones transitorias

- Sobretensión por rayo: Para formas de onda de 1,2/50μs, que requieren una capacidad de resistencia instantánea entre 2 y 4 veces superior.

- Sobretensión de conmutación: En equipos electrónicos de potencia, cuando dv/dt > 1000 V/μs, corriente de desplazamiento deben tenerse en cuenta.

Técnicas topológicas avanzadas para placas de circuito impreso de alta tensión y densidad

6.1 Optimización de la distancia de fuga en 3D

Relación de fuga efectiva = (recorrido real de la superficie) / (distancia en línea recta)- Optimización de ranuras en V: Cuando la relación profundidad/anchura de la ranura es > 1,5, la relación de fuga efectiva puede alcanzar 2,0-3,0.

- Muros de aislamiento vertical: Las paredes de FR4 con un espesor de> 0,8 mm pueden soportar 8-10 kV/mm.

6.2 Diseño de gradientes para placas de circuito impreso de tensión mixta

- Control del gradiente de campo eléctrico: La diferencia de tensión entre conductores adyacentes debe ser de transición sin problemasevitando cambios bruscos > 300 V/mm.

- Disposición de la zona protegida: Establecer 2-3mm "zonas sin cobre" entre las zonas de alta y baja tensión, relleno de material dieléctrico protector.

Evolución de las normas y tendencias futuras

7.1 Suplementos de las normas emergentes

- IEC 62368-1: Sustituye a 60950-1, introduciendo el concepto de clasificación de las fuentes de energía.

- IPC-9592: Requisitos específicos para los convertidores de potencia, centrados en fallos sinérgicos térmico-eléctricos.

7.2 Diseño del espaciado mediante simulación

- Simulación del campo eléctrico por elementos finitos: Identifica zonas de concentración de campos eléctricos, optimizando para ahorrar 20-30% de espacio en comparación con los métodos estándar.

- Análisis de acoplamiento multifísico: Simulación combinada de tensiones eléctricas, térmicas y mecánicas para predecir la fiabilidad a largo plazo.

Marco de verificación del diseño y evaluación de la fiabilidad

8.1 Estrategia de pruebas aceleradas

- Pruebas de sesgo de temperatura y humedad (THB)85°C / 85% RH / Tensión nominal, evaluando la tasa de decaimiento de la resistencia de aislamiento.

- Pruebas de esfuerzo por etapas: Aumento de la tensión en 10-20% pasos para identificar avería blanda umbrales.

8.2 Tecnologías de vigilancia en línea

- Detección de descargas parciales: Detecta los niveles de descarga en el rango de pC, proporcionando una alerta temprana de la degradación del aislamiento.

- Control en línea de la resistencia del aislamiento: Monitorización en tiempo real de la resistencia a nivel GΩ.

Conclusión

El diseño del espaciado de las placas de circuito impreso de alto voltaje está experimentando un cambio de paradigma de normas empíricas a predicción basada en modelosy hacia optimización inteligente. Entre las orientaciones futuras figuran:

- Base de datos de materiales y correspondencia de inteligencia artificial: Recomendación automática de materiales de sustrato y espaciado en función de las condiciones de funcionamiento.

- Verificación de gemelos digitales: Los prototipos virtuales validan la racionalidad del espaciado mediante simulación multifísica.

- Diseño adaptativo: Ajuste dinámico de los parámetros de funcionamiento basado en la información de los sensores para compensar el envejecimiento del aislamiento.

Los ingenieros de diseño deben establecer un perspectiva de seguridad a nivel de sistemasunificando el diseño del espaciado con consideraciones gestión térmica, estructura mecánica y protección medioambiental. Al conseguir un profundo conocimiento de la física del fracaso en lugar de limitarse a cumplir las normas, se puede lograr un funcionamiento fiable de los productos electrónicos de alta tensión en entornos cada vez más difíciles.