Herstellung von Halbleiter-Leiterplatten

& Montage Dienstleistungen

Ultrahohe Lagenzahl, Präzisionsimpedanz und fortschrittliche thermische Lösungen für ATE-Lastplatinen, Burn-in-Platinen und Probe Card-Schnittstellen.

Warum sollten Sie uns für Halbleiter-Leiterplatten wählen?

Wir liefern die extreme Präzision und Materialleistung, die für komplexe Prüfung integrierter Schaltungen erforderlich sind, bei denen Signalintegrität und thermische Zuverlässigkeit nicht verhandelbar sind.

Ultra-hohe Schichtdicke

Fachkundige Herstellung von Leiterplatten mit hoher Lagenzahl (bis zu 50+ Lagen) mit komplexen Blind-, Buried- und Stacked-Microvia-Architekturen.

Präzise Impedanzkontrolle

Hochentwickelte TDR-Tests, die enge Impedanztoleranzen (±5% bis hinunter zu ±2% auf Anfrage) für Ultra-High-Speed-Signalpfade gewährleisten.

Fortschrittliche thermische Materialien

Arbeit mit speziellen Substraten (Rogers, Megtron 6/7, Tachyon 100G), die eine hohe Verlustleistung in Burn-in-Umgebungen ermöglichen.

Micro-Pitch BGA-Bestückung

SMT-Bestückung für BGA- und CSP-Bauteile im Raster von 0,3 mm bis 0,4 mm, unerlässlich für Halbleiterschnittstellen mit hoher Pinzahl.

Back-Drilling Mastery

Interne Präzisionsbohrungen zur Beseitigung von Signalstummeln und zur Minimierung von Reflexionen bei Hochfrequenz-ATE-Anwendungen.

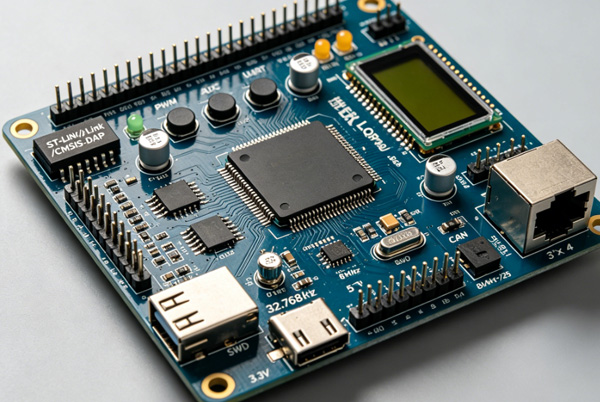

Bewertung bis Produktion

Nahtloser Übergang von kundenspezifischen Evaluation Boards (EVB) zur Massenproduktion von Burn-In Boards (BIB) und Load Boards.

Elite-Engineering für Hochgeschwindigkeits-Chip-Tests

Unsere Spezialisten für Halbleitertechnik arbeiten mit IC-Design- und Testteams zusammen, um die kritische Schnittstelle zwischen dem Chip und und den automatisierten Testgeräten (ATE) zu optimieren und so die Signalintegrität und den Ertrag zu maximieren.

Strategische Signalführung und Isolierung zum Schutz vor Übersprechen und Beeinträchtigung der Datenverbindung.

Auswahl hybrider Materialien (z. B. FR4 + High-Speed Rogers), um ein Gleichgewicht zwischen Kosten und extrem verlustarmer Leistung herzustellen.

Fortgeschrittene Wärmeableitungsanalyse für leistungsstarke KI- und Serverchips unter Testbedingungen.

Strenge Designprüfungen gewährleisten die Herstellbarkeit der dichtesten Leiterplattenarchitekturen der Branche.

Fertigungskapazitäten für Halbleiter-PCB

TopfastPCB bietet die für den Lebenszyklus von Halbleitern erforderliche Hardware mit extremen Spezifikationen, von der anfänglichen Siliziumbewertung bis zum massiven Burn-in und den Tests auf Systemebene.

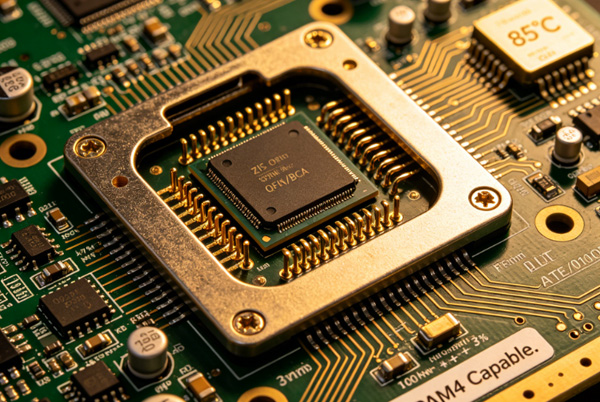

ATE-Lasttafeln

Mehrschichtige Präzisionsimpedanzplatten, die IC-Muster mit automatisierten Hochgeschwindigkeitsprüfgeräten verbinden.

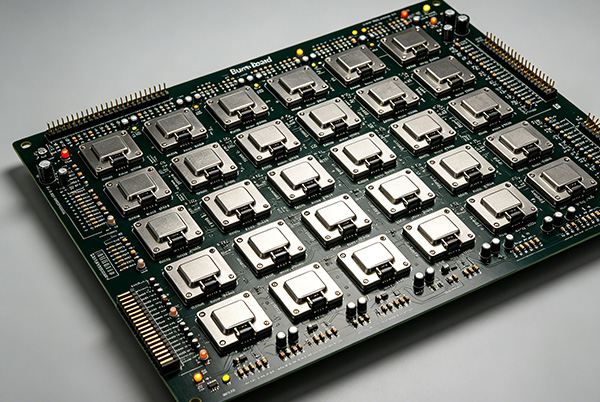

Einbrenn-Bretter (BIB)

Zuverlässige Hochtemperaturplatinen, die für Langzeit-Screening und thermische Belastungstests entwickelt wurden.

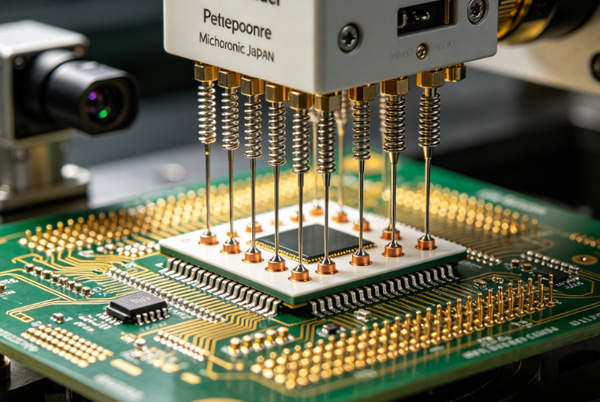

Probe Card PCB

Ultraflache Schnittstellen-Leiterplatten für Probe-Card-Baugruppen, die direkte Halbleitertests auf Wafer-Ebene ermöglichen.

Workflow in Halbleiterqualität

Expertenprüfung für komplexe Schichtzahlen und exotische Materialaufbauten.

Integriertes Back-Drilling und TDR-Impedanzkontrolle für Sub-Path-Integrität.

Elite-Bestückung für Fine-Pitch-BGA- und High-Pin-Count-Teststecker.

Validierung des gesamten Spektrums zur Gewährleistung von Null-Signalverbindungsverlusten bei IC-Tests.

Unterstützung für den Lebenszyklus von Halbleitern

TopfastPCB unterstützt die weltweit führenden Chiphersteller, TopfastPCB liefert wichtige Schnittstellenhardware für jede Phase des Halbleitertestzyklus.

Innovationszentrum für Präzisions-IC-Tests

Unsere hochmoderne Produktionsstätte ist für die extremen Schichtzahlen und Signalleistung optimiert, die für die Halbleiterprüfung erforderlich ist, und bietet TDR- und thermische Verifizierung der Spitzenklasse.

Ausgewählt von den führenden Chipherstellern der Welt

Innovative IC-Designer, globale IDMs und führende ATE-Ausrüster vertrauen auf TopfastPCB für ihre anspruchsvollste Testhardware.

Halbleiter PCB FAQ

Häufige Fragen zur Herstellung von IC-Testplatinen, Impedanzkontrolle und ATE-Normen.

Fragen Sie einen Spezialisten →Wir nutzen branchenführende Fertigungstechnologien, um Platinen mit mehr als 50 Lagen herzustellen. Diese Fähigkeit ist für komplexe Halbleiter-Lastplatinen und Sondenkarten, die ein massives paralleles Routing und dedizierte Stromversorgungsebenen erfordern, unerlässlich.

Wir bieten eine Standard-Impedanzkontrolle mit ±5%. Für ultrakritische Hochfrequenzpfade in der ATE- und Hochgeschwindigkeits-IC-Evaluierung können wir mit verifizierten Materialstapeln und fortschrittlichen TDR-Tests Präzisionstoleranzen von bis zu ±2% erreichen.

Ja. Wir verwenden Präzisionslaser und mechanisches Rückbohren, um überflüssige Platinenstummel zu entfernen. Dies ist eine wichtige Voraussetzung für ATE-Lastkarten, um saubere Signale zu gewährleisten und die Reflexion bei Frequenzen über 10 GHz zu minimieren.

Für leistungsstarke KI- und Server-Chips entwickeln wir Platinen mit dicken Kupferschichten (bis zu 12 Unzen) und Metallkerneinsätzen oder Kupfer-Münz-Technologie, um die extremen thermischen Belastungen zu bewältigen, die bei lang andauernden Burn-in-Zyklen entstehen.